Odgovori na ispitna pitanja iz UOAR2

Table of Contents

- 1. Iskazna logika

- 2. Minimizacija logičkih izraza

- 3. Tranzistori i logička kola

- 4. Kombinatorna kola

- 5. Sekvencijalna kola

- 6. Arhitektura i organizacija

- 7. Adresiranje

- 8. Assembler

- 9. Procesor

- 10. Memorija

- 11. Cache

- 12. Magistrale

- 13. Sistem prekida

- 14. I/O

- 15. Virtuelna memorija

- 16. Napredne arhitekture

- 17. Verilog

1 Iskazna logika

- Napisati istinitosne tablice osnovnih logičkih veznika (NE, I, ILI)

NE

A NE(A) 1 0 0 1 I

A B I(A, B) 1 1 1 1 0 0 0 1 0 0 0 0 ILI

A B ILI(A, B) 1 1 1 1 0 1 0 1 1 0 0 0

- Napisati istinitosne tablice izvedenih logičkih veznika (NI, NILI, EILI)

NI (NAND)

A B NI(A, B) 1 1 0 1 0 1 0 1 1 0 0 1 NILI (NOR)

A B NILI(A, B) 1 1 0 1 0 0 0 1 0 0 0 1 EILI (XOR)

A B EILI(A, B) 1 1 0 1 0 1 0 1 1 0 0 0

- Navesti bar jedan način na koji se EILI veznik može predstaviti pomoću osnovnih logičkih veznika (NE, I, ILI)

- Preko KNF-a (A ili ne(B)) i (ne(A) ili B)

Navesti osnovne zakone algebre logike

Algebra logike je uređena šestorka \((S, \cdot, +, \bar{}, 1, 0)\)

- \(S\) - neprazan skup

- \(\cdot, +\) - binarne operacije

- \(\bar{}\) - unarna operacija

\(1, 0\) - izdvojeni elementi skupa \(S\)

Osnovni zakoni:

- Asocijativnost

- \((x \cdot y) \cdot z = x \cdot (y \cdot z)\)

- \((x + y) + z = x + (y + z)\)

- Neutral

- \(x \cdot 1 = x\)

- \(x + 0 = x\)

- Komplementarnost

- \(x \cdot \bar{x} = 0\)

- \(x + \bar{x} = 1\)

- Komutativnost

- \(x \cdot y = y \cdot x\)

- \(x + y = y + x\)

- Distributivnost

- \(x \cdot (y + z) = x \cdot y + x \cdot z\)

- \(x + (y \cdot z) = (x + y) \cdot (x + z)\)

- Asocijativnost

Zbog čega se algebra logike koristi kao osnova savremenih računara?

Iz razloga što je mnogo jednostavnije, stabilnije i jeftinije napraviti fizički uređaj koji ima dva diskretna stanja nego više njih. Takođe, aritmetičke operacije nad binarnim brojevima je jednostavno opisati pomoću algebre logike i samim tim implementirati pomoću logičkih kola.

Šta znači da su dva logička izraza ekvivalentna?

Znači da su im vrednosti pri istim valuacijama promenljivih iste odnosno da za istu kombinaciju vrednosti “ulaznih” promenljivih daju isti “izlaz”

- Definisati pojmove elementarne konjunkcije i disjunktivne normalne forme (DNF). Šta je savršena elementarna konjunkcija, a šta savršena DNF?

- Literal je logički izraz koji je ili logička promenljiva ili negacija logičke promenljive (eg. \(x, \bar{y}\))

- Elementarna konjunkcija je logički izraz koji se sastoji iz konjunkcije literala (eg. \(x\bar{y}z\bar{p}\))

- Savršena elementarna konjunkcija sadrži tačno jedan literal za svaku logičku promenljivu (eg. \(P = \{x, y, z\}, S = \bar{x} \cdot y \cdot z\))

- DNF je logički izraz koji se sastoji od disjunkcije elementarnih konjunkcija (eg. \(x\bar{y} + \bar{x} + xyz\))

- Savršena DNF se sastoji od disjunkcije savršenih elementarnih konjunkcija (eg. \(P = \{x, y, z\}, SDNF = x\bar{y}z + \bar{x}yz + xyz\))

- Definisati pojmove elementarne disjunkcije i konjunktivne normalne forme (KNF). Šta je savršena elementarna disjunkcija, a šta savršena KNF?

- Literal je logički izraz koji je ili logička promenljiva ili negacija logičke promenljive (eg. \(x, \bar{y}\))

- Elementarna disjunkcija je logički izraz koji se sastoji iz disjunkcije literala (eg. \(x + \bar{y} + z\bar{p}\))

- Savršena elementarna disjunkcija sadrži tačno jedan literal za svaku logičku promenljivu (eg. \(P = \{x, y, z\}, \bar{x} + y + z\))

- KNF je logički izraz koji se sastoji od konjunkcije elementarnih disjunkcija (eg. \((x + \bar{y}) \cdot (\bar{x} + y) \cdot (x + y + z)\))

- Savršena KNF se sastoji od konjunkcije savršenih elementarnih disjunkcija (eg. \(P = \{x, y, z\}, SKNF = (x + \bar{y} + z) \cdot (\bar{x} + y + z) \cdot (x + y + z)\))

- Ukratko opisati postupak za svođenje logičkog izraza na DNF

- Eleminisanje logičkih konstanti - primena veznika nad 0 i 1 sve dok se izraz ne svede na 0 ili 1 ili ostane bez konstanti

- De Morganovi zakoni i dupla negacija

- Distributivnost \(\cdot\) prema \(+\) - nakon ovog koraka dobijamo DNF

- Za svođenje na KNF važe prethodna dva koraka, dok je treći distributivnost \(+\) prema \(\cdot\)

- Idempotentnost, neutral, apsorpcija - primenom ovih (i drugih zakona) moguće je dodatno minimizovati DNF

Šta je logička funkcija i koliko ima funkcija reda \(n\)?

Logička funkcija je svako preslikavanje \(f: \{0, 1\}^{n} \rightarrow \{0, 1\}\) koja logičke vrednosti \((x_{1}, x_{2}, ..., x_{n})\) slika u logičku vrednost \(y \in \{0, 1\}\). Kardinalnost domena logičkih funkcija reda \(n\) je \(2^{n}\), dok je kodomena \(2\), dakle, pošto se svaka funkcija iz domena može slikati u dve vrednosti u kodomenu, postoji \(2^{2^{n}}\) funkcija reda \(n\)

Šta je potpun sistem veznika? Navesti bar tri primera potpunih sistema logičkih veznika

Potpun sistem veznika predstavlja skup veznika pomoću kojeg je moguće predstaviti svaku logičku funkciju. Primeri:

- I, ILI, NE

- I, NE

- ILI, NE

- NI (Šeferov veznik: \(\uparrow\))

- NILI (Pirsov/Lukašijevičev veznik: \(\downarrow\))

- Izraziti NE, I i ILI veznik pomoću NI veznika

- NE(x) = NI(x, x)

- I(a, b) = NE(NI(a, b)) = NI(NI(a, b), NI(a, b))

- ILI(a, b) = NE(I(NE(a), NE(b))) = …

Ukratko objasniti kako se proizvoljna logička funkcija može izraziti u obliku izraza u savršenoj DNF

Čitajući tablicu logičke funkcije, ako je izlaz za neku valuaciju 1, onda na našu savršenu DNF formulu dodajemo novi konjunkt koji se sastoji iz konjunkcije literala koji za tu valuaciju daju vrednost 1.

2 Minimizacija logičkih izraza

Šta je minimizacija logičkih izraza i zbog čega nam je značajna?

Minimizovati logički izraz znači pronaći logički ekvivalentan izraz koji sadrži najmanji mogući broj veznika.

Najčešće nam koristi pri dizajnu logičkih kola kako bismo smanjili cenu proizvodnje, ali suštinski može da služi za rešavanje mnogo šire grupe problema koji se mogu mapirati u SAT problem.

Na primeru objasniti metod algebarskih transformacija za minimizaciju logičkih izraza.

Koristimo dva pravila:

- Grupisanje: \[ K_{1} = x \cdot K' \\ K_{2} = \bar{x} \cdot K' \\ \downarrow \\ K = K'(x + \bar{x}) = K' \\ \]

- Udvajanje:

- U slučaju da imamo konjunkte \(K_{1}, K_{2}\) nad kojima bismo mogli da primenimo grupisanje sa \(K\), onda dupliramo \(K\) da bismo mogli da grupišemo sa oba

Primer:

\[F(x, y, z) = x\bar{y}z + \bar{x}\bar{y}z + x\bar{y}\bar{z}\]

Možemo grupisati prvi i drugi kao i prvi i treći, tako da ćemo primeniti prvo udvajanje pa tek onda grupisanje

\[F(x, y, z) = x\bar{y}z + \bar{x}\bar{y}z + x\bar{y}z + x\bar{y}\bar{z}\] \[F(x, y, z) = \bar{y}z(x + \bar{x}) + x\bar{y}(z + \bar{z})\] \[F(x, y, z) = \bar{y}z(x + \bar{x}) + x\bar{y}(z + \bar{z})\] \[F(x, y, z) = \bar{y}z + x\bar{y}\]

Objasniti način upotrebe Karnoovih mapa za minimizaciju logičkih izraza. Primer.

Fali slika ili nešto slično

Karnoove mape predstavljaju grafički metod za minimizaciju logičkih izraza koji funkcioniše po principu grupisanja. Nakon što nacrtamo tabelu gde se susendna polja (susedstvo se gleda kao da je tabela zapravo površina torusa) razlikuju za jednu vrednost (Grejov kod) popunimo mesta koja u tabeli daju \(1\) kao rezultat. Minimizujemo tako što prvo pokušamo da obuhvatimo sve \(1\) u pravougaonik od \(16\) elemenata, zatim redom \(8\), \(4\), \(2\), \(1\). Posmatramo promenljive u okviru jednog pravougaonika koje se nisu promenile i njih stavljamo u finalnu minimizovanu DNF formulu.

Objasniti metodu Kvin-Meklaskog za minimizaciju logičkih izraza. Primer.

Fali slika ili nešto slično

Metoda Kvin-Meklaskog je metoda minimiacije logičkih izraza koja je pogodna za implementaciju na računaru.

- Na ulazu dobijamo funkciju u SDNF. Sortiramo rastuće savršene konjunkcije po broju neinvertovanih literala i izdelimo ih u klase, gde \(i\) -ta klasa sadrži SK koji imaju \(i\) neinvertovanih literala.

- Vršimo grupisanje elemenata iz \(i\) -te sa elementima iz \(i + 1\) -ve klase, i rezultat čuvamo za sledeću iteraciju. Grupisanje je moguće ako se elementi koji se porede razlikuju samo na jednom mestu. Ovo radimo sve dok je moguće grupisati.

- Formiramo tabelu prostih implikanata (vidi primer). Identifikujemo bitne proste implikante.

Kako se upotrebljavaju Karnoove mape u prisustvu nebitnih vrednosti? Primer.

Fali slika ili nešto slično

Kada imamo nebitne (don’t care) vrednost, njih možemo da tretiramo onako kako nama odgovara, odnosno ako nam omogućavaju da zaokružimo veću površinu tretiramo ih kao \(1\), u suprotnom nema potrebe da ih zaokružimo.

Kako se metod Kvin-Meklaskog koristi u prisustvu nebitnih vrednosti? Primer.

Fali slika ili nešto slično

U prvoj fazi algoritma se nebitne vrednosti tretiraju kao \(1\), odnosno učestvuju u grupisanju.

U drugoj fazi algoritma se nebitne vrednosti tretiraju kao \(0\), tj. ne navode se u tabeli prostih implikanata.

Šta je Petrikov metod i koja je njegova uloga u okviru metode Kvin-Mekalskog? Primer.

TODO

Petrikov metod je metod koji se koristi za pronalaženje najmanjeg podskupa preostalih prostih implikanata u slučaju da neka kolona ostane “nepokrivena” u metodi Kvin-Mekalskog.

3 Tranzistori i logička kola

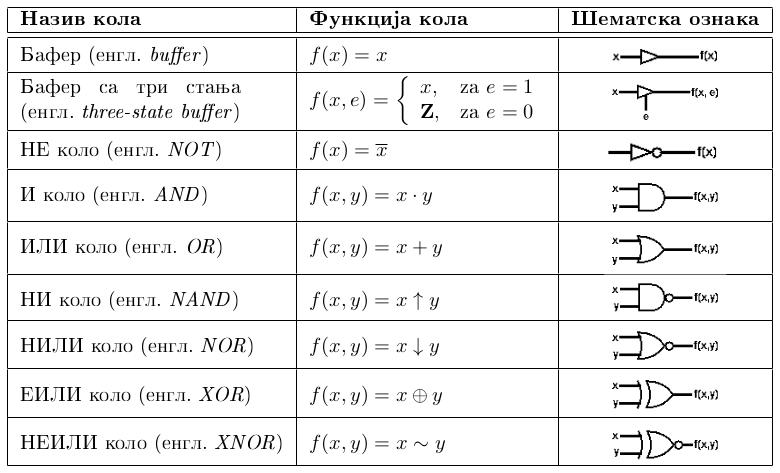

Elementarna logička kola (gejtovi) i njihove šematske oznake.

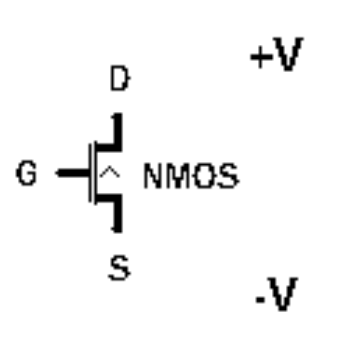

Nacrtati simbol i objasniti funkciju NMOS tranzistora.

NMOS tranzistor ima 3 ulaza:

- Source - povezan sa negativan napon

- Drain - povezan na pozitivan napon

- Gate - odredjuje da li će struja proticati

- Ako je napon u zoni logičke nule onda je izlaz vrednost visoke impendanse

- Ako je napon u zoni logičke jedinice onda je izlaz 1

G S D 0 0 \(Z\) 1 0 0 NMOS tranzistor ima ulogu u donjoj mreži (pulldown network) prekidača da poveže masu (ground) sa izlazom da bi u slučaju niske voltaže na izlazu bila 0

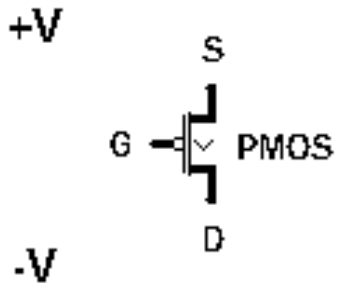

Nacrtati simbol i objasniti funkciju PMOS tranzistora.

PMOS tranzistor ima 3 ulaza:

- Source - povezan sa pozitivan napon

- Drain - povezan na negativan napon

- Gate - odredjuje da li će struja proticati

- Ako je napon u zoni logičke nule onda je izlaz 1

- Ako je napon u zoni logičke jedinice onda je izlaz vrednost visoke impendanse

G S D 0 1 1 1 1 \(Z\) PMOS tranzistor ima ulogu u gornjoj mreži (pullup network) prekidača da poveže napajanje (supply) sa izlazom da bi u slučaju visoke voltaže na izlazu bila 1

Implementacija NE kola u CMOS-u

Fali slika ili nešto slično

- Ako je ulaz 0 samo iz PMOS-a tranzistora će izlaziti struja koja predstavlja 1

- Ako je ulaz 1 samo iz NMOS-a tranzistora će izlaziti struja koja predstavlja 0

- Dakle, biće upaljen samo tranzistor koji je potreban, čime se postiže ušteda u potrošnji i smanjuje grejanje komponenti.

Implementacija NI i I kola u CMOS-u

Fali slika ili nešto slično

Donja mreža se implementira rednim povezivanjem dva NMOS tranzistora čime se postiže da se 0 dobije samo kada su oba ulaza 1

Gornja mreža se implementira paralelnim povezivanjem dva PMOS tranzistora čime se postiže da se 1 dobija samo kada je barem jedan od ulaza 0 (čime se takođe osigurava da pri ulazu 1 1 pušta samo donja mreža “da radi”)

I se dobija tako što se na NI nadoveže NE

Implementacija NILI i ILI kola u CMOS-u

Fali slika ili nešto slično

NILI se implementira po istom principu kao NI, s tim što su ovde NMOS tranzistori povezani paralelno, dok su PMOS povezani redno.

Gornja mreža se implementira rednim povezivanjem dva PMOS tranzistora čime se postiže da se 1 dobije samo kada su oba ulaza 0

Donja mreža se implementira paralelnim povezivanjem dva NMOS tranzistora čime se postiže da se 0 dobija samo kada je barem jedan od ulaza 1 (čime se takođe osigurava da pri ulazu 0 0 pušta samo gornja mreža “da radi”)

ILI se dobija tako što se na NILI nadoveže NE

Implementacija EILI kola u CMOS-u

Za bilo koju logičku funkciju ideja je da se za mesta u tablici gde se dobija 0 na izlazu gleda kako da se napravi donja mreža pomoću NMOS tranzistora (rednim ili paralelnim povezivanjem). Analogno za gornju mrežu i PMOS tranzistore.

Fali slika ili nešto slično

Donja mreža se implementira pomoću 4 redno-paralelna NMOS tranzistora čiji ulazi su \(X\) i \(Y\) s leve i \(\bar{X}\) i \(\bar{Y}\) s desne strane čime se 0 dobija samo akko su \(X\) i \(Y\) isti

Gornja mreža se implementira pomoću 4 redno-paralelna PMOS tranzistora čiji ulazi su \(X\) i \(\bar{Y}\) s leve i \(\bar{X}\) i \(Y\) s desne strane čime se 1 dobijamo samo akko su \(X\) i \(Y\) različiti

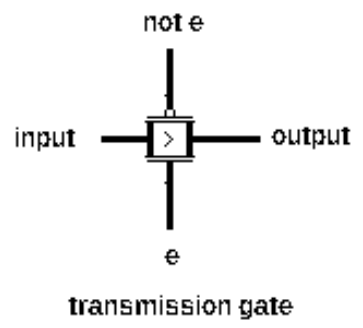

Propusni tranzistori i prenosne kapije. Funkcija i uloga.

Propusne tranzistore koristimo u slučaju da nam je potrebno uslovno propuštanje nekog signala. Ako koristimo samo NMOS tranzistor imaćemo problem sa propuštanjem signala 1 jer neće postojati velika razliku u naponu između source-a i gate-a. Analogno za samo PMOS i signal 0.

Da bismo to rešili, koristimo prenosne kapije koje su spoj ova dva propusna tranzistora. Često se koriste i za realizaciju bafera sa 3 stanja.

Šta je bafer sa tri stanja i čemu služi?

Bafer sa 3 stanja je kombinatorno logičko kolo koje služi za pojačavanje stanja i uslovno/kontrolno propuštanje signala.

Implementacija bafera sa tri stanja u CMOS-u.

Fali slika ili nešto slično

Implementacija zavisi od toga šta nam je potrebno, i koje signale imamo na raspolaganju. U slučaju da nam nije potrebno pojačavanje signala neće nam trebati dvostruki inverter. Povezujemo ulazni signal, kontrolni signal i njegovu negaciju sa prenosnom kapijom čime i implementiramo bafer sa tri stanja.

Šta je vrednost visoke impendanse i koja je njena uloga u logičkim kolima?

Vrednost visoke impendanse odgovara tipu

NULLu nekim višim programskim jezicima, odnosno predstavlja odsustvo vrednosti. Označavamo je sa \(Z\) i koristimo je na primer u slučaju da imamo dva kola koja se povezuju na isti ulaz, kako ne bismo imali vrednosti u konfliktu, jedna od njih ima vrednost visoke impendanse.

4 Kombinatorna kola

Šta je kombinatorno kolo?

Kombinatorno kolo je logičko kolo čije vrednosti na izlazima se mogu sračunati u bilo kom trenutku u zavisnosti od ulaznih vrednosti odnosno prethodne ulazne vrednosti ne utiču na novu izlaznu vrednost.

- Navesti najvažnije vrste osnovnih kombinatornih kola.

- Multipleksori (Mux) i demultipleksori (DeMux)

- Koderi i dekoderi

- Komparatori

- Pomerači

- Sabirači i oduzimači

4.1 Multipleksor i demultipleksor

Šta je multipleksor i koja mu je osnovna funkcija? Predstaviti grafičkim simbolom i tablicom multipleksor 4-1.

Fali slika ili nešto slično

Multipleksor \(2^{k}-1\) je kombinatorno kolo koje omogućava selekciju nekog od \(k\) ulaza pomoću selekcionih bitova, čime faktički igra istu ulogu kao

if elsekonstrukt u višim programskim jezicima.S I 00 \(U_{0}\) 01 \(U_{1}\) 10 \(U_{2}\) 11 \(U_{3}\) Nacrtati logičko kolo implementacije multipleksora 4-1.

Fali slika ili nešto slično

- Možemo implementirati direktno

- Disjunkcija 4 konjunkcije od po 3 signala

- U svakoj konjunkciji su vezani odgovarajući signali u zavisnosti od rednog broja (npr. za \(U_{0}\) imamo konjunkciju od \(U_{0}, \bar{S_{1}}, \bar{S_{0}}\), za \(U_{1}\) imamo konjunkciju od \(U_{1}, S_{1}, \bar{S_{0}}\))

- Možemo implementirati pomoću multipleksora 2-1

- Možemo implementirati direktno

Kako se multipleksor upotrebljava za implementaciju logičkih funkcija?

Fiksiranjem jedne ili više vrednosti, jednu “veliku” funkciju dekomponujemo na dve ili više manjih koje biramo pomoću multipleksora.

Šta je demultipleksor i koja je njegova osnovna funkcija? Predstaviti grafičkim simbolom i tablicom demultipleksor 1-4.

Fali slika ili nešto slično

Demultipleksor je kombinatorno kolo koje igra obrnutu ulogu u odnosu na multipleksor, odnosno ima \(1\) ulaz koji preusmerava na \(2^{k}\) izlaza u zavisnosti od vrednosti selekcionih bitova.

U nepopunjenim ćelijama tabele može biti \(0\) ili \(Z\) u zavisnosti od implementacije.

S \(I_{0}\) \(I_{1}\) \(I_{2}\) \(I_{3}\) 00 \(U_{0}\) 01 \(U_{0}\) 10 \(U_{0}\) 11 \(U_{0}\) Nacrtati logičko kolo implementacije demultipleksora 1-4.

Fali slika ili nešto slično

- Možemo implementirati direktno

- Možemo implementirati pomoću demultipleksora 1-2

4.2 Koder i dekoder

Šta je dekoder i koja je njegova osnovna funkcija? Predstaviti grafičkim simbolom i tablicom dekoder 2-4.

Fali slika ili nešto slično

Dekoder je kombinatorno kolo koje na osnovu vrednosti binarnog broja aktivira odgovarajući signal na izlazu. Najčešće se koristi pri dekodiranju mašinskih instrukcija.

Eg. Ako pretpostavimo da imamo 16 registara, u samoj instrukciji možemo kodirati koje registre koristimo samo preko 4 bita. Dekoder služi za “prevođenje” koje registre želimo da učestvuju.

S \(I_{0}\) \(I_{1}\) \(I_{2}\) \(I_{3}\) 00 1 0 0 0 01 0 1 0 0 10 0 0 1 0 11 0 0 0 1 Nacrtati logičko kolo implementacije dekodera 2-4.

Fali slika ili nešto slično

Praktično isto kao i demultipleksor 1-4 (direktna implementacija) s tim što je ovde binarna konjunkcija i nemamo ulaz već samo kontrolne bitove.

Šta je koder i gde se obično koristi? Šta je koder sa prioritetom?

Fali slika ili nešto slično

Koder je kombinatorno kolo koje \(2^{k}\) ulaza mapira u \(k\) -bitni broj (pod pretpostavkom da je najviše jedan ulaz 1). Takođe imamo i kontrolni izlaz koji nas obaveštava u slučaju da nijedan ulaz nije 1.

Običan koder ne može da handle-uje slučaj kada je više od jednog ulaza 1. Iz tog razloga svakom od ulaza se pridodaje težina, što omogućava da na izlazu bude ulaz sa najvišim prioritetom.

Možemo koristiti koder se prioritetom pri obradi signala prekida. U slučaju da više uređaja zahteva pažnju procesora, možemo odrediti indeks uređaja koji traži pažnju a najvišeg je prioriteta.

Nacrtati logičko kolo implementacije kodera 4-2.

Fali slika ili nešto slično

Implementacija ima smisla kad se pogleda tabela (namerno su naopačke indeksi)

\(U_{3}\) \(U_{2}\) \(U_{1}\) \(U_{0}\) \(I_{1}\) \(I_{0}\) 0 0 0 1 0 0 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 0 1 1 Nacrtati logičko kolo implementacije kodera 4-2 sa prioritetom.

Fali slika ili nešto slično

Ne kapiram crtež moraću u nekoj knjizi to da vidim verovatno

4.3 Komparator

Šta je komparator? Navesti osnovne vrste komparatora.

Komparator je kombinatorno kolo koje služi za upoređivanje dva podatka.

Vrste:

- Komparatori za jednakost

- Komparatori za potpuno poređenje

Nacrtati logičko kolo 4-bitnog komparatora (za poređenje na jednakost)

Fali slika ili nešto slično

Bitovi se redom porede tako što se XOR-uju i na kraju povežu sa NILI gejtom koje će dati \(1\) ako su svi ulazi \(0\), u suprotnom \(0\)

Nacrtati logičko kolo 4-bitnog komparatora za potpuno poređenje

Fali slika ili nešto slično

Koristimo 4-bitni oduzimač čiji rezultat šaljemo na NILI koje nam govori da li su ulazi jednaki i carry bit koji nam govori da li je \(x\) manji od \(y\), u suprotnom kad su oba \(0\), \(x\) je veći od \(y\)

4.4 Pomerač

Nacrtati logičko kolo 8-bitnog pomerača (ulevo)

Fali slika ili nešto slično

Pošto je 8-bitni pomerač, maksimalno je moguće pomeriti ga 7 puta.

Ideja je da se pomoću 8-bitnih 2-1 multipleksora u zavisnosti od kontrolnih bitova prvo proba da se pomeri za 4 pa za 2 pa za 1, čijim kombinacijama je moguće dobiti vrednosti pomeranja između 0 i 7. Pomeranje se vrši tako što se u multipleksorima ručno poveže ulaz pomeren za \(2^{i}, i = 0,1,2\) bitova.

4.5 Sabirači i oduzimači

Nacrtati istinitosnu tablicu i logičko kolo binarnog polusabirača

Fali slika ili nešto slično

\(x\) \(y\) \(S\) \(C\) 1 1 0 1 1 0 1 0 0 1 1 0 0 0 0 0 Iz čega se vidi da je \(S\) zapravo XOR od \(x\) i \(y\), a \(C\) AND.

Nacrtati istinitosnu tablicu i logičko kolo binarnog sabirača

Fali slika ili nešto slično

\(x\) \(y\) \(pc\) \(S\) \(C\) 1 1 1 1 1 1 1 0 0 1 1 0 1 0 1 1 0 0 1 0 0 1 1 0 1 0 1 0 1 0 0 0 1 1 0 0 0 0 0 0 Možemo implementirati ili preko dva polusabirača ili direktno. Preko dva polusabirača je lakše.

Višebitni talasasti sabirač. Kašnjenje.

Ulančavanjem manjih sabirača koji zavise od svog prethodnika kako bismo dobili sabirač za veći broj bitova dolazimo u situaciju da kašnjenje raste linearno u odnosu na broj bitova. Talasasti sabirač znači da se talasasto računa zbir počevši od sabirača zaduženog za najniže bitove ka višim.

Nacrtati istinitosnu tablicu i logičko kolo binarnog poluoduzimača

Fali slika ili nešto slično

\(x\) \(y\) \(S\) \(C\) 1 1 0 0 1 0 1 0 0 1 1 1 0 0 0 0 Nacrtati istinitosnu tablicu i logičko kolo binarnog oduzimača

Fali slika ili nešto slično

\(x\) \(y\) \(pc\) \(S\) \(C\) 1 1 1 1 1 1 1 0 0 0 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 0 1 0 1 1 0 0 1 1 1 0 0 0 0 0 Višebitni talasasti oduzimač. Kašnjenje.

Ulančavanjem manjih oduzimača koji zavise od svog prethodnika kako bismo dobili oduzimač za veći broj bitova dolazimo u situaciju da kašnjenje raste linearno u odnosu na broj bitova. Talasasti oduzimač znači da se talasasto računa razlika počevši od sabirača zaduženog za najniže bitove ka višim.

Objasniti ukratko princip rada sabirača sa računanjem prenosa unapred.

CLA= Carry Lookahead AdderCLAsabirači problem računanja zbira dva broja rade tako što efikasno pretprocesiraju u \(O(logN)\) vremenu, \(N\) - broj bitova, da li će biti prenosa na individualnom bitu i samim tim, sabiranje je moguće izvršiti paralelno nad svim bitovima čime je ukupna vremenska složenost sabiranja svedena na \(O(logN)\) za razliku od \(O(N)\) kod talasastog sabirača.Šta kod sabirača sa računanjem prenosa unapred označavaju vrednosti \(P_{i}\) i \(G_{i}\) i po kojim se formulama računaju?

Koristeći činjenicu da prenos na \(i\) -tom bitu zavisi od toga da li \(i\) -ti bitovi generišu prenos ili prenose prethodni prenos, dobijamo formulu:

\[C_{0} = x_{0}y_{0} + x_{0}pc + y_{0}pc = x_{0}y_{0} + (x_{0} + y_{0})pc\] što možemo dodatno svesti na \[C_{0} = x_{0}y_{0} + (x_{0} \oplus y_{0})pc\] jer ako su \(x\) i \(y\) jednaki \(1\) svakako će zbog prethodne disjunkcije rezultat biti isti

- \(G_{i} = x_{i}y_{i}\) - govori nam da li \(i\) -ti bit generiše prenos

- \(P_{i} = x_{i} \oplus y_{i}\) - govori nam da li \(i\) -ti bit propagira prethodni prenos

Finalno, imamo /rekurentnu jednačinu: \[ C_{i} = G_{i} + P_{i}C_{i - 1} \\ C_{0} = G_{0} + P_{0}pc \]

Navesti formule po kojima CLA (Carry Look Ahead) jedinica računa prenose \(C_{i}\) kao i grupne \(P\) i \(G\) vrednosti.

\[ C_{i} = G_{i} + P_{i}C_{i - 1} \\ C_{0} = G_{0} + P_{0}pc \\ \] \(K\) - broj bitova \[ G_{G} = G_{K - 1} + G_{K - 2}P_{k} + G_{K - 3}P_{K - 2}P_{K - 1} + ... + G_{0}P_{1}P_{2}\cdot ... \cdot P_{K - 1}\] \[ G_{G} = \sum_{i = 0}^{K - 1}G_{i}\prod_{j = i + 1}^{K - 1}P_{j}\] \[ P_{G} = P_{0}P_{1} \cdot ... \cdot P_{K - 1}\] \[ P_{G} = \prod_{i = 0}^{K - 1}P_{i}\]

Grupne vrednost nam služe da bismo lakše računali pri hijerarhijskom kombinovanju za višebitne ulaze.

Fiksirajmo \(K = 4\)

Četvorobitni sabirač će generisati prenos akko njegova najviša pozicija generiše prenos (\(G_{3}\)) ili ako \(G_{2}\) ali se i prenese preko najvišeg (\(P_{3}\)) ili ako \(G_{1}P_{2}P_{3}\) ili ako \(G_{0}P_{1}P_{2}P_{3}\).

Četvorobitni sabirač će preneti \(pc\) akko svi njegovi elementi prenose

4.6 Implementacija ALU i opšta kombinatorna kola

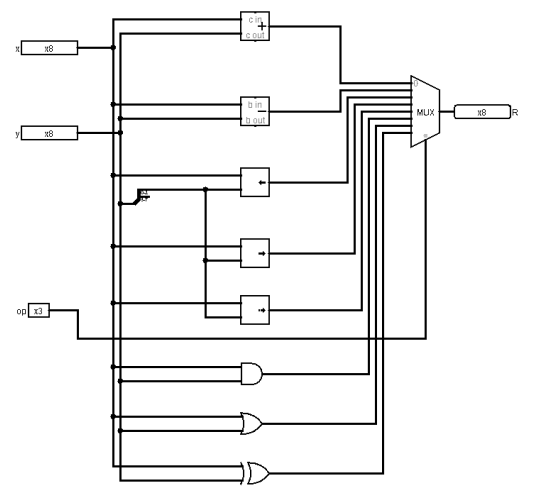

Navesti primer implementacije ALU jedinice.

Nacrtaj kolo koje prima dva 8-bitna ulaza i 3-bitni \(op\) ulaz koji specificira koju operaciju treba izvršiti. Stavi bilo kojih 8 operacija i poveži rezultate sa

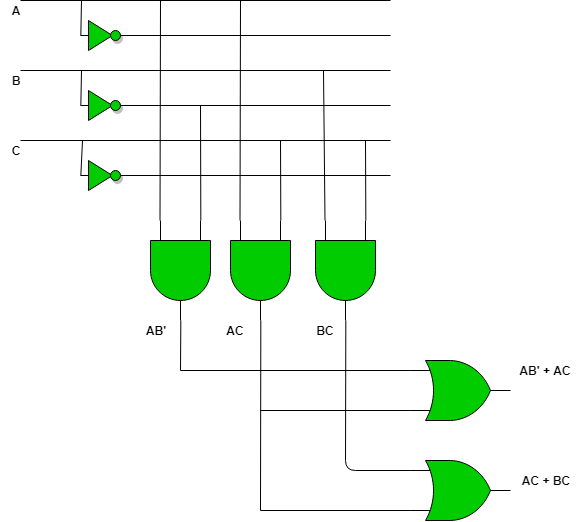

mux-om koji za selekcione bitove uzima \(op\).Šta je programibilni niz logičkih elemenata (PLA)? Navesti primer

Programibilni niz logičkih elemenata je programibilni logički uređaj (PLD) koji ima programibilne AND zatim i OR gejtove.

Koristimo ih u slučaju da imamo fiksan skup “retkih” / “raštrkanih” (sparse) logičkih funkcija (funkcije sa mnogo 0) i želimo jednostavno i jeftino kolo koje će njih računati.

Primer procesa pravljenja PLA-a:

- Funkcije koje želimo da računamo u PLA-u predstavimo u SDNF

- neka su te funkcije u SDNF:

- \(F_{1} = x\bar{y}\bar{z} + x\bar{y}z + xyz\)

- \(F_{2} = \bar{x}yz + x\bar{y}z + xyz\)

- neka su te funkcije u SDNF:

- Minimizujemo ih

- dobijamo:

- \(F_{1} = x\bar{y} + xz\)

- \(F_{2} = yz + xz\)

- dobijamo:

- Koliko imamo promeljivih toliko će nam input buffer-a trebati (input buffer nam daje njegov ulazni signal i njegovu negaciju)

- Programibilno povezujemo AND gejtove sa izlazima input buffer-a u zavisnosti od konjunkta prisutnih u funkcijama

- Imaćemo 3 različita konjunkta (\(x\bar{y}, xz, yz\)), dakle trebaće nam 3 AND gejta

- Programibilno povezujemo ILI gejtove sa AND gejtovima tako da dobijemo željene funkcije

Neki drugi primer:

- Funkcije koje želimo da računamo u PLA-u predstavimo u SDNF

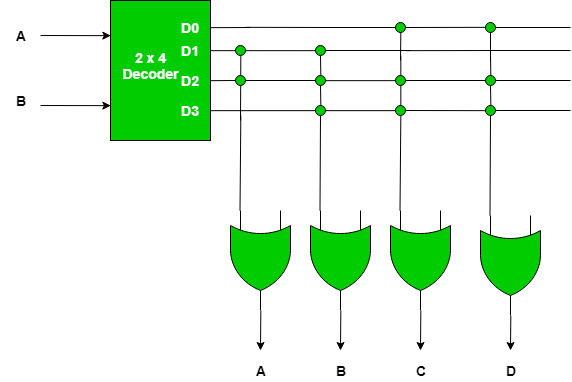

Kako se pomoću kombinatornih mreža implementira neizmenjiva memorija (ROM)? Primer tablice i odgovarajuće implementacije.

Na ulazu se dobija adresa koja se potom prosleđuje ka dekoderu koji aktivira odgovarajuće izlaze na koje su povezani ulazi disjunkcija. U zavisnosti od povezanosti izlaza dekodera i ulaza disjunkcija određujemo koje podatke ćemo čitati iz ROM memorije.

adr out 11 0011 10 1100 01 1111 00 0111

5 Sekvencijalna kola

Šta je sekvencijalno kolo? Po čemu se sekvencijalna kola razlikuju od kombinatornih kola?

Sekvencijalno kolo je logičko kolo koje daje izlaz na osnovu trenutnog ulaza i prethodnih izlaza.

Za razliku od sekvencijalnih, kombinatorna kola nemaju interno stanje koje se čuva u memoriji, stoga za isti ulaz uvek daju isti izlaz, što nije slučaj sa sekvencijalnim kolima.

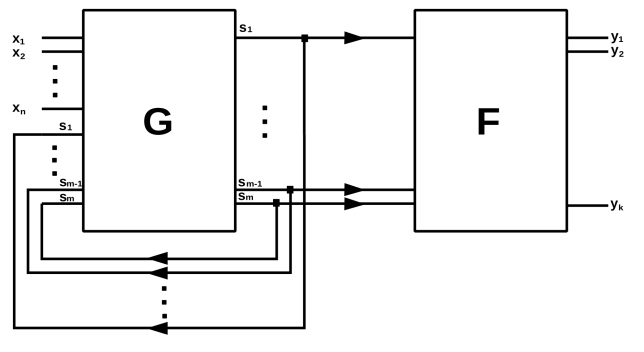

Nacrtati konceptualni dijagram sekvencijalnog kola i objasniti osnovni princip rada.

- \(G\) je kombinatorno kolo koje po principu povratne sprege održava stanje \(S\) (\(G\) se može posmatrati kao vektorska funkcija \(G: X \times S \rightarrow S\), za \(X\) skup svih ulaza i \(S\) skup svih stanja)

- \(S\) se neće promeniti sve dok se \(X\) ne promeni

- \(F\) je kombinatorno kolo koje transformiše stanje \(S\) u izlaz \(Y\) (\(F\) se može posmatrati kao vektorska funkcija \(F: S \rightarrow Y\) za \(S\) skup svih stanja i \(Y\) skup svih izlaza)

- \(G\) je kombinatorno kolo koje po principu povratne sprege održava stanje \(S\) (\(G\) se može posmatrati kao vektorska funkcija \(G: X \times S \rightarrow S\), za \(X\) skup svih ulaza i \(S\) skup svih stanja)

- Šta je nestabilnost sekvencijalnog kola, a šta nedeterminističnost? Šta je metastabilnost?

- Nestabilnost sekvencijalnog kola je pojava oscilovanja kola između različitih stanja

- Nederminističnost sekvencijalnog kola je pojava odlaženja u neko “nasumično” stabilno stanje u zavisnosti od fizičkih faktora

- Metastabilnost sekvencijalnog kola je pojava stabilizacije u nekom nevalidnom međustanju

Šta je funkcija (tablica) prelaska sekvencijalnog kola? Navesti primer.

To je vektorska logička funkcija koja deterministički definiše prelaz sa jednog stabilnog stanja u drugo stabilno stanje na osnovu prethodnog stanja i novog ulaza.

Funkcija prelaska za SR reze:

S R Q Qnext 0 0 0 0 0 0 1 1 0 1 - 0 1 0 - 1 1 1 - ? -označava bilo koju vrednost?označava nedefinisanu vrednost

Objasniti ulogu časovnika. Na koji način časovnik omogućava sinhronizaciju sekvencijalnih kola?

Časovnik istom frekvencijom izbacuje naizmenično signale 0 i 1 što se koristi za sinhronizaciju sekvencijalnih kola. Postavljanjem frekvencije časovnika na dovoljnu tako da najsporije sekvencijalno kolo uspe da se dovede u stabilno stanje, omogućava da se vreme posmatra diskretno, što olakšava rezonovanje o sekvencijalnim kolima i omogućava jednostavnu sinhronizaciju. Svako kolo povezano na časovnik prima njegov signal, i svoje promene vrši isključivo kad signal časovnika to dozvoli.

Objasniti razliku između sinhronih i asinhronih sekvencijalnih kola.

Sinhrona sekvencijalna kola zavise od zajedničkog signala odnosno časovnika, koji svima diktira kada je moguće izvršiti promene stanja, dok asinhrona moraju eksplicitno da naprave komplikovane međusobne veze kako bi uskladile kada je dozvoljeno kojem kolu da izvrši promene stanja.

- Elementi ciklusa časovnika. Tipovi časovnika. Frekvencija časovnika.

- Elementi ciklusa časovnika:

- Pozitivan deo ciklusa = vreme trajanja \(1\)

- Negativan deo ciklusa = vreme trajanja \(0\)

- Tipovi časovnika:

- Simetrični = pozitivan deo ciklusa traje isto koliko i negativan

- Asimetrični = različito traju pozitivan i negativan deo ciklusa

- Frekvencija časovnika = broj ciklusa u jednoj sekundi

- Elementi ciklusa časovnika:

5.1 Reze i flip-flopovi

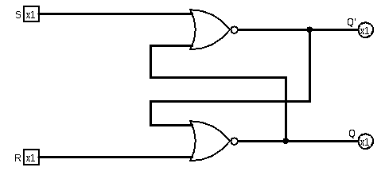

Šta je SR reza? Nacrtati implementaciju, tablicu prelaska, logički simbol i objasniti ponašanje.

SR reza je asinhrono memorijsko kolo koje ima mogućnost čuvanja jednobitnog stanja.

\(S\) \(R\) \(Q\) \(Q^{next}\) 0 0 0 0 0 0 1 1 0 1 - 0 1 0 - 1 1 1 - ? SR reza funkcioniše tako što postavljanjem \((S, R) = (0, 1)\) resetujemo sačuvanu vrednost odnosno čuvamo \(0\), analogno za \((S, R) = (1, 0)\) setujemo \(1\). Kada imamo \((S, R) = (0, 0)\), tada nam izlaz ostaje zapamćena vrednost. Problem sa SR rezom je što kolo ne može da bude stabilno pri ulazu \((S, R) = (1, 1)\)

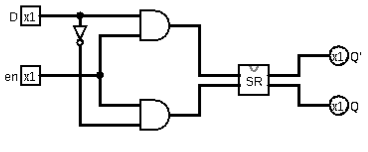

Šta je D reza? Nacrtati implementaciju, tablicu prelaska, logički simbol i objasniti ponašanje.

D reza je asinhrono memorijsko kolo koje ima mogućnost čuvanja jednobitnog stanja.

\(D\) \(e\) \(Q\) \(Q^{next}\) - 0 0 0 - 0 1 1 0 1 - 0 1 1 - 1 Imajući u vidu da SR reza ima problem sa nedozvoljenim ulazom \((S, R) = (1, 1)\), jedan od načina na koji bi to moglo da se reši jeste da se uvede ulaz \(D\) (data) koji se direktno povezao sa \(S\), dok bi se njegova negacija na \(R\), čime bi se izgubila mogćnost “čitanja memorije” odnosno stanja \((S, R) = (0, 0)\) zbog čega se uvodi i ulaz \(e\) (enable) koji se pre povezivanja sa \(S\) odnosno \(R\) konjuguje sa \(D\) odnosno \(\bar{D}\).

Koja je osnovna razlika između reze i flip-flopa?

Reza je asinhrono sekvencijalno kolo dok je flip-flop povezan na časovnik odnosno sinhrono sekvencijalno kolo.

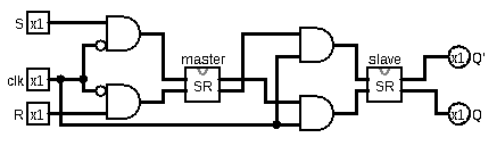

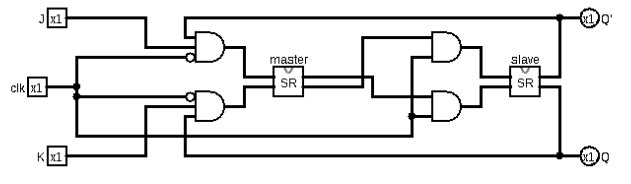

Nacrtati implementaciju master-slave SR flip-flopa i objasniti ponašanje

Imamo dve SR reze, leva je master, desna je slave. Izlazi master-a se prosleđuju i čuvaju u slave-u. Ulazi obe reze kontrolisani su konjunkcijama koje su povezane na signal časovnika. Kada je signal časovnika \(0\), tada su ulazi master-a otvoreni i moguće je menjati vrednost koja se čuva u njemu, dok su ulazi slave-a zatvoreni. Pri uzlaznom rubu ulazi master-a se zatvaraju dok se ulazi slave-a otvaraju i upisuje se ono što je bilo u master-u i na kraju to isto i daje na izlazu. Posledica toga je da do promene stanja može doći isključivo u uzlaznom rubu.

U prethodnom objašnjenju je pretpostavljena implementacija koja menja stanje u uzlaznom rubu, suprotnim invertovanjem signala časovnika je moguće implementacija koja menja stanje u silaznom rubu.

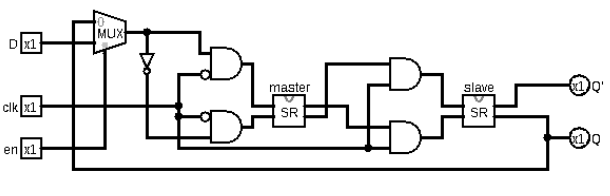

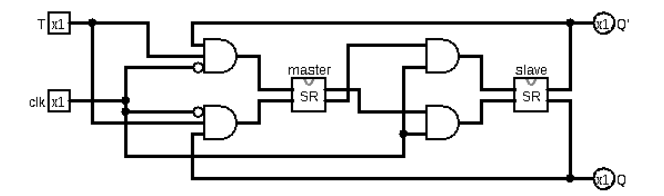

Nacrtati implementaciju master-slave D flip-flopa i objasniti ponašanje

Imamo dve SR reze, leva je master, desna je slave. Izlazi master-a se prosleđuju i čuvaju u slave-u. Ulazi obe reze kontrolisani su konjunkcijama koje su povezane na signal časovnika. Kada je signal časovnika \(0\), tada su ulazi master-a otvoreni i moguće je menjati vrednost koja se čuva u njemu, dok su ulazi slave-a zatvoreni. Pri uzlaznom rubu ulazi master-a se zatvaraju dok se ulazi slave-a otvaraju i upisuje se ono što je bilo u master-u i na kraju to isto i daje na izlazu. Posledica toga je da do promene stanja može doći isključivo u uzlaznom rubu.

Kao i kod D reze eliminiše se slučaj \((S, R) = (1, 1)\) (negiranjem izlaza multipleksora). Takođe se dodaje i multipleksor koji u zavisnosti od \(e\) bira da li da propusti stari signal ili D.

Nacrtati implementaciju master-slave JK flip-flopa i objasniti ponašanje

Imamo dve SR reze, leva je master, desna je slave. Izlazi master-a se prosleđuju i čuvaju u slave-u. Ulazi obe reze kontrolisani su konjunkcijama koje su povezane na signal časovnika. Kada je signal časovnika \(0\), tada su ulazi master-a otvoreni i moguće je menjati vrednost koja se čuva u njemu, dok su ulazi slave-a zatvoreni. Pri uzlaznom rubu ulazi master-a se zatvaraju dok se ulazi slave-a otvaraju i upisuje se ono što je bilo u master-u i na kraju to isto i daje na izlazu. Posledica toga je da do promene stanja može doći isključivo u uzlaznom rubu.

JK flip-flop rešava problem \((S, R) = (1, 1)\) tako što na konjunkcije ispred ulaza master-a dovodi i izlaze slave-a koji će uvek biti različiti, i time se semantika \((S, R) = (1, 1)\) menja na invertovanje stanja.

Nacrtati implementaciju master-slave T flip-flopa i objasniti ponašanje

Imamo dve SR reze, leva je master, desna je slave. Izlazi master-a se prosleđuju i čuvaju u slave-u. Ulazi obe reze kontrolisani su konjunkcijama koje su povezane na signal časovnika. Kada je signal časovnika \(0\), tada su ulazi master-a otvoreni i moguće je menjati vrednost koja se čuva u njemu, dok su ulazi slave-a zatvoreni. Pri uzlaznom rubu ulazi master-a se zatvaraju dok se ulazi slave-a otvaraju i upisuje se ono što je bilo u master-u i na kraju to isto i daje na izlazu. Posledica toga je da do promene stanja može doći isključivo u uzlaznom rubu.

T flip-flop je praktično JK flip-flop gde su \(J\) i \(K\) spojeni u jedan ulaz, čime je semantika takva da registar može ili da čuva tekuće stanje ili da ga invertuje.

Objasniti problem “hvatanja jedinice” (1s cathing problem) kod master-slave SR i JK flip-flopova. Na koji način se ovaj problem može rešiti?

Kada imamo kratkotrajni šum signala (npr. nagli skok i pad) na jednom od ulaza, u fazi časovnika u kojoj se menjaju vrednosti, kod SR, JK i T flip-flopova se zabeleži \(1\) iako se u međuvremenu promenilo na \(0\). Do toga dolazi jer se \(1\) odmah pamti u \(master\) -u da bi pri promeni na \(0\) to samo dalo signal da se ono što je zapamćeno održi.

Moguće je rešiti problem tako što se SR, JK ili T flip-flop svedu na D flip-flop koji ne pati od istog problema tako što se uvede multipleksor koji u zavisnosti od ulaza polaznog flip-flopa bira šta će se dalje propustiti.

5.2 Statička i dinamička memorija

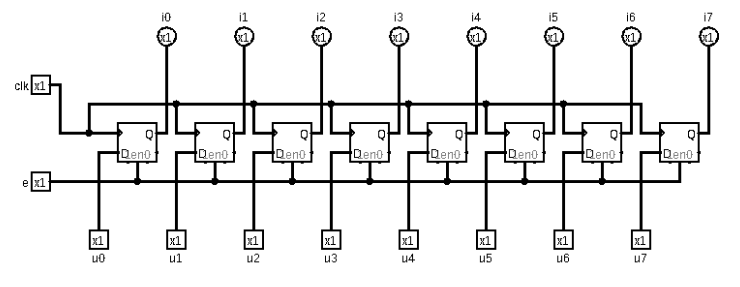

Šta je registar i kako se implementira? Navesti primer.

Registar dužine \(n\) je kolo koje čuva \(n\) -bitnu vrednost. Najčešće se implementira preko D flip-flopova koji su svi povezani na zajednički signal časovnika i \(e\) signal.

Statička memorija. Primer realizacije memorije \(4\times4\).

Statička memorija se najčešće koristi za implementaciju procesorskih registara i keš memorije.

\(4 \times 4\) memorija se sastoji iz \(4\) reda od po \(4\) registra, gde \(4\) registra predstavljaju jednu adresu.

I/O:

- \(adr\) - adresa nad kojom treba operisati

- \(data_{in}\) - podatke sa kojima treba raditi

- \(data_{out}\) - pročitani podaci

- \(wr\) - flag koji označava dozvoljeno pisanje

- \(rd\) - flaag koji označva dozvoljeno čitanje

- \(clk\) - signal od časovnika

Pisanje:

- \(adr\) se prosleđuje dekoderu

- rezultat se prosleđuje u konjunkciju sa \(wr\)

- to stvara signal \(e\) za sve flip-flopove u tom redu

- podaci iz \(data_{in}\) bivaju upisani u adresu \(adr\)

Čitanje:

- \(adr\) se prosleđuje dekoderu

- rezultat aktivira bafere sa 3 stanja

- dodatni baferi sa 3 stanja se aktiviraju u zavisnosti od \(rd\)

- podaci sa adrese \(adr\) bivaju poslati na \(data_{out}\)

Na primeru objasniti princip konstrukcije većih memorija pomoću manjih.

Fali slika ili nešto slično

Efikasna realizacija memorijske ćelije kod statičkih memorija.

Da bismo smanjili cenu i kašnjenje signala i ujedno povećali efikasnost težimo da smanjimo broj komponenti potreban za realizaciju nekog kola.

Kod asinhronih memorija, gde koristimo reze, bismo mogli umesto D-reza da “izvučemo” zajedničko NE za jednu kolonu i koristimo SR reze sa dodatnim ulazom \(e\). Na ovaj način smanjujemo broj NE gejtova sa \(mn\) na \(n\).

Kod sinhronih memorija, gde koristimo flip-flopove u master-slave organizaciji, tada bismo mogli umesto da svaki flip-flop ima svog master-a uvedemo jednog master-a za jednu kolonu, koji će dalje naći svog slave-a pomoću dekodera. Potrebna su i \(2\) reza koja će da pamte adresu. Na ovaj način smanjujemo broj potrebnih reza sa \(2mn\) na \(mn + n + 2\), što je značajna ušteda.

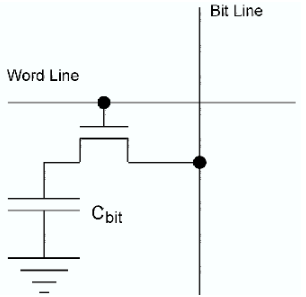

Objasniti princip rada memorijske ćelije kod dinamičkih memorija.

Svaka ćelija za čuvanje jednog bita se sastoji iz jednog tranzistora i kondenzatora. Vrednost bita se čuva naelektrisanjem kondenzatora. Pun kondenzator odgovara \(1\), dok prazan odgovara \(0\). Kada želimo da upišemo vrednost, na bitsku liniju dovodimo odgovarajuću vrednost i aktiviramo liniju reči čime se otvara tranzistor i zbog toga se kondenzator puni ili prazni u zavisnosti od vrednosti koju želimo da upišemo. Prilikom čitanja bitska linija se naelektriše na neki međupotencijal (npr. 2.5V), pa se aktivira linija reči zbog čega će se potencijal na liniji reči blago promeniti u odnosu na vrednost koja je sačuvana, što će pojačavač registrovati i “pojačati” ka 0V ili 5V. Prilikom čitanja uništavamo zapisanu vrednost, tako da je potrebno nakon čitanja da je opet i upišemo. Kondenzator se vremenom sam prazni, tako da je potrebno periodično vršiti osvežavanje kompletne memorije.

Prednosti i nedostaci dinamičkih memorija u odnosu na statičke.

Prednosti:

- Manji broj tranzistora i komponenti, dakle manja cena

Mane:

- Dosta sporije čitanje i pisanje u odnosu na statičke

- Komplikovaniji proces sinhronizacije zbog većeg broja mogućih operacija nad memorijom

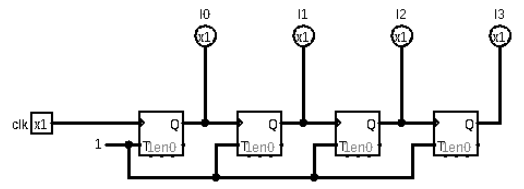

Šta je pomerački registar i gde se obično koristi?

Pomerački registar je niz flip-flopova (izlaz flip-flopa \(i\) je ulaz od \(i + 1\)) povezanih na isti časovnik koji pomeraju niz bitova ulevo ili udesno sa svakim ciklusom časovnika.

Najčešće se upotrebljavaju za konvertovanje iz paralelnog u serijski vid komunikacije i obratno.

5.3 Binarni brojač

Asinhroni binarni brojač. Nacrati šemu i objasniti princip rada. Koji je osnovni nedostatak asinhronih brojača?

Implementiramo ga preko nekoliko T flip-flopova tako što je onaj koji čuva bit najniže vrednosti direktno povezan na signal časovnika. Svi T flip-flopovi za ulaz primaju \(1\). Izlaz \(N - 1\) -og T flip-flopa predstavlja signal časovnika, što znači da do promene dolazi samo ako je signal časovnika prešao sa \(1\) na \(0\), zbog čega se javlja “talasasti” efekat odnosno kašnjenje je \(O(N)\), za \(N\) - broj T flip-flopova.

Glavni nedostatak je vremenska neefikasnost.

Sinhroni binarni brojač. Nacrtati šemu i objasniti princip rada.

Implementiramo ga preko nekoliko JK flip-flopova tako što ih povežemo sve sa časovnikom. Odluku da li da menjamo \(i\) -ti flip-flop donosimo na osnovu konjunkcije izlaza svih prethodnih flip-flopova. Na ovaj način nam se usložnjvaju AND gejtovi, zbog čega je kašnjenje \(O(logN)\), za \(N\) - broj JK flip-flopova.

Dizajn brojača sa proizvoljnim redosledom stanja. Primer.

Fali slika ili nešto slično

U slučaju da nam je potrebno da imamo brojač koji neće ići po “default” redosledu, već nekim našim, potreban nam je brojač sa proizvoljnim redosledom stanja.

- Nacrtamo konačni automat kao graf prelaska stanja

- Prebacimo to u tablični oblik i odredimo vrednosti \(J_{i}\) i \(K_{i}\) potrebne za svaki prelazak stanja

- Preko Karnoovih mapa minimizujemo za svako \(J_{i}\) i \(K_{i}\)

5.4 Konačni automati i transduktori

Konačni automati i transduktori kao model sinhronih sekvencijalnih kola. Dizajn konačnih transduktora. Primer.

Fali slika ili nešto slično

Konačni automat je model ponašanja sinhronih kola koji se sastoji od konačnog skupa stanja i prelaza između stanja i pridruženih akcija.

Ukoliko to kolo prilikom svake promene stanja generiše novu vrednost na izlazu, onda to kolo nazivamo konačni transduktor.

Konačni transduktori predstavljaju opšti model sinhronih sekvencijalnih kola.

- Definišemo tablicu prelaska

- \(Q\) - trenutno stanje

- \(X\) - ulaz

- \(Q^{next}\) - sledeće stanje

\(Y\) - izlaz

\(Q\) \(X\) \(Q^{next}\) Y 0 0 1 0 0 1 2 0 1 0 1 1 1 1 3 1 2 0 0 0 2 1 2 1 3 0 1 0 3 1 0 1

- Nacrtamo graf

- Stanja su čvorovi

- Grane su usmerene od trenutnog ka sledećem stanju

- “Težine” su formata \(X/Y\), odnosno ako smo na stanju \(Q\) sa ulazom \(X\) preći ćemo na \(Q^{next}\) i na izlazu ispisati \(Y\)

- Definišemo tablicu prelaska

Ukratko objasniti osnovni princip dizajna kontrolne jedinice kao konačnog transduktora.

Konačni transduktor je model ponašanja sinhronih kola koji se sastoji od konačnog skupa stanja, prelaza između stanja i pridruženih akcija.

Prelaz je opisan uslovom koji neophodno da bude ispunjen da bi došlo do prelaza.

Akcija je opis aktivnosti koja se sprovodi prilikom nekom prelaza.

Može se predstaviti kao usmereni graf, ali se češće predstavlja putem tablice.

Kontrolna jedinica se može modelovati kao konačni transduktor koji na ulazu ima

IR(trenutna instrukcija) iPSW(trenutni flegovi i sl) registre a na izlazu kontrolne signale. Da ne bismo nagađali logiku uCUkoristimo konačni transduktor kao model koji je moguće fizički implementirati nadPLA, koji je dalje moguće minimizovati, ili u vidu mikrokoda.- Navesti primer opisa nekog algoritma u formi konačnog transduktora (samo tablica prelaska, bez realizacije samog transduktora)

- \(Q\) - trenutno stanje

- \(X\) - ulaz

- \(Q^{next}\) - sledeće stanje

\(Y\) - izlaz

\(Q\) \(X\) \(Q^{next}\) Y 0 0 1 0 0 1 2 0 1 0 1 1 1 1 3 1 2 0 0 0 2 1 2 1 3 0 1 0 3 1 0 1

6 Arhitektura i organizacija

- Šta je arhitektura a šta organizacija računara?

- Arhitektura računara je apstraktni model koji opisuje računar iz ugla programera kog zanima koje instrukcije postoje, načini adresiranja, kako se predstavljaju podaci i sl.

- Odgovara na pitanje Šta radi računar?

- Organizacija računara je implementacija arhitekture gde se posmatraju veze između komponenti, low-level opis kako se određene operacije obavljaju

- Odgovara na pitanje Kako radi računar?

- Arhitektura računara je apstraktni model koji opisuje računar iz ugla programera kog zanima koje instrukcije postoje, načini adresiranja, kako se predstavljaju podaci i sl.

Šta obuhvata ISA (instruction set architecture)?

ISA obuhvata:

- koje instrukcije postoje

- koji načini upravljanja memorijom hardver podržava (načine adresiranja, virtuelna memorija, konzistentnost memorije)

- kako se predstavljaju podaci

Šta su troadresni procesori? Primer instrukcija i koda. Karakteristike.

Troadresni procesor je procesor koji u instrukciji može da ima tri adrese. Programi na troadresnom računaru su kompaktni, ali same instrukcije mogu da budu glomazne zbog zahteva za čuvanjem 3 operanda.

ADD C, A, B MUL C, A, B

Šta su dvoadresni procesori? Primer instrukcija i koda. Karakteristike.

Dvoadresni procesori su procesori koji mogu da imaju maksimalno dve adrese u instrukciji. Rezultat operacije se upisuje u neku privremenu lokaciju ili u lokaciju jednog od operanada. Smanjuje se dužina programa, ubrzava izvršavanje, ali se ponekad koristi dodatna memorija.

LOAD T, A ; T = A ADD B, T ; B += T

Šta su jednoadresni procesori? Primer instrukcija i koda. Karakteristike.

Jednoadresni procesori su procesori koji imaju jednu adresu u instrukciji. Operacije koje zahtevaju dva operanda se razrešavaju tako što je druga adresa implicitna. Ovi računari se često obraćaju memoriji za upis i čitanje međurezultata. Programi su dosta dugački i izvršavanje je relativno sporo. Koriste se u situacijama kada je memorija dosta skupa.

LOAD A ; učitaj A u akumulator ADD B ; acc += B STORE A ; A = acc

Šta su nuloadresni procesori? Primer instrukcija i koda. Karakteristike.

Nuloadresni procesori su procesori gde je maksimalan broj adresa u instrukciji \(0\) osim kod instrukcija

PUSHiPOP. Takvi procesori implicitno adresiraju svoje operande (često stavljajući ih na stek), što predstavlja veliko ograničenje, pa se koriste samo u specijalnim slučajevima.PUSH A PUSH B ADD POP

Objasniti odnos performansi i broja adresa.

Instrukcije sa većim brojem adresa su moćnije, programi kompaktniji i veća je brzina izvršavanja. S povećanjem broja adresa raste i složenost instrukcije što otežava konstrukciju procesora i produžava vreme potrebno za prepoznavanje operacionog koda.

Šta je

LOAD/STOREarhitektura? Objasniti.Sve operacije se izvršavaju isključivo nad registrima procesora. Samo operacije

LOADiSTOREmogu da pristupaju memoriji.RISCi vektorski procesori često koriste ovakvu arhitekturu. Prednost je smanjenje složenosti dekodiranja zbog manjeg broja instrukcija.Karakteristike

CISCarhitekture.Ciljevi:

- složena arhitektura skupa instrukcija

- raznovrsnost operacija

- raznovrsnost načina adresiranja itd.

Posledice:

- Iz velikog skupa instrukcija se koristi oko 20%, dok se ostale ređe koriste

- Otežano dekodiranje zbog velikog broja instrukcija i načina adresiranja

Karakteristike

RISCarhitekture.Ciljevi:

- jednostavna arhitektura skupa instrukcija

- obezbeđivanje minimalnog skupa instrukcija i načina adresiranja

- povećan broj registara koji se mogu koristiti za računanje

Posledice:

- stalniji skup instrukcija

- jednostavno dekodiranje

- kraće trajanje izvršavanja

- jednostavnija implementacija procesora

Odnos

RISCiCISCarhitektura.Danas procesori najčešće predstavljaju hibride ove dve arhitekture.

RISC>CISC:- jednostavnija konstrukcija zbog manjeg broja instrukcija

- manje vremena je potrebno za izradu samog procesora

- bolje performanse jer je lakše definisati prevodioce koji formiraju optimalniji kod nego

CISCprocesori

CISC>RISC:- veća količina softvera je napisana za

CISCarhitekturu

- Struktura i format mašinske instrukcije

- strukturu čine:

- operacioni kod

- operandi

- format instrukcije određuje način kodiranja ranijepomenutih komponenti u binarnom obliku (implicitno određuje i dužinu instrukcije)

- strukturu čine:

- Vrste operanada mašinske instrukcije

- Registarski

- Memorijski

- Neposredni (konstante)

7 Adresiranje

Objasniti direktno adresiranje memorijskih operanada.

Stvarna adresa se direktno uključuje u instrukciju. Adrese koje se javljaju u ovom načinu adresiranja se još nazivaju i apsolutne adrese. Ovaj način adresiranja je relativno jednostavan jer nema izračunavanja adrese, a prenos operanada zahteva samo jedno referisanje memorije.

Objasniti indirektno adresiranje memorijskih operanada.

Kod indirektnog adresiranja je poznata samo adresa lokacije na kojoj se nalazi adresa operanda, pa se do te adrese dolazi indirektno, tj. instrukcija sadrži binarni kod regista procesora čija se vrednost koristi kao adresa memorijskog operanda. Ovaj način adresiranja zahteva dva ciklusa, jedan za čitanje adrese, drugi za čitanje samog operanda.

- Objasniti indeksno adresiranje memorijskih operanada.

- Bazno indeksno adresiranje:

- Instrukcija sadrži binarne kodove dva registra čije se vrednosti sabiraju i tako dobijamo adresu memorijskog operanda. Obično je vrednost jednog registra fiksirana, a drugi predstavlja indeks koji se pomera i koji je moguće množiti konstantom (npr. \(4\) ili \(8\)) pre sabiranja sa baznim registrom. Korisno je za pristup elementima niza.

- Apsolutno indeksno adresiranje:

Bazna adresa ne mora biti u registru, već može biti zadata kao apsolutna adresa na koju se dodaje vrednost indeksnog registra (uz eventualno prethodno skaliranje)

add eax, table[4 * esi] ; table je niz koji se nalazi u data segmentu

- Bazno indeksno adresiranje:

Objasniti relativno adresiranje memorijskih operanada.

U ovom načinu za adresiranje se koristi brojač instrukcija (

PCprogram counter) čiji sadržaj se uzima kao početna adresa. U adresni deo instrukcije se upisuje ceo broj koji predstavlja udaljenje od početne adrese. Relativno adresiranje se koristi kada znamo da je ciljana adresa negde u okolini tekuće.Objasniti načine adresiranja na x86-64 arhitekturi.

Načini adresiranja opisuju kako se određuje operand instrukcije.

Neposredno za konstante:

mov rax, 42

Registarsko:

mov rax, rdi- Memorijsko:

Direktno

.data value dw 42 ... f: add eax, value

Indirektno

; rdi je pokazivač na prvi element niza add eax, [rdi]

Indeksno

; rdi je pokazivač na prvi element niza mov rsi, 3 add eax, [rdi + 4 * rsi]

Objasniti načine adresiranja na ARM arhitekturi.

Načini adresiranja opisuju kako se određuje operand instrukcije.

Neposredno za konstante:

mov r0, r0, 42

- Registarsko:

Direktno

mov r0, r1Indirektno

; r1 je pokazivač na prvi element niza ldr r0, [r1]

- Indeksno

Prefiksno bez update-a

; r1 je pokazivač na prvi element niza mov r2, #3 ldr r0, [r1, r2, lsl #2] ; r0 = *(r1 + 4 * r2)

Prefiksno sa update-om

; r1 je pokazivač na prvi element niza mov r2, #3 ldr r0, [r1, r2, lsl #2]! ; r1 = r1 + 4 * r2; r0 = *r1;

Postfiksno sa update-om

; r1 je pokazivač na prvi element niza mov r2, #3 ldr r0, [r1], #4 ; r0 = *r1; r1 = r1 + 4;

8 Assembler

- Instrukcije transfera. Funkcija i primer upotrebe. (x86-64, ARM)

x86-64mov, movzx, movsxdest- registar

- memorija

src- konstanta

- registar

memorija

mov dest, src ; kopira iz src u dest movzx dest, src ; kopira iz src u dest i proširuje 0 movsx dest, src ; kopira iz src u dest i proširaje znakom

leadest- registar

src- konstanta

- registar

memorija

lea dest, src ; kopira adresu od src u dest

ARMldr/strldr: Učitava vrednost sa adrese u registarstr: Čuva vrednost registra na adresiop{<cond>}{<size>} Rn, <adress><cond> = {eq: =, gt: >, ge: >=, lt: <, le: <=}<size> = {'': word, b: byte, h: halfword}

ldm/stmldm: Učitava vrednosti u više registara počevši od adresestm: Čuva vrednosti više registara počevši od adreseop{<adrr_mode>}{<cond>} Rn{!}, <reg_list><adrr_mode> = {IA: increment_after, DB: decrement_before}<cond> = {eq: =, gt: >, ge: >=, lt: <, le: <=}! updateuje Rn za\(\pm 4 \cdot len(reg\_list)\)u zavisnosti od <adrr_mode><reg_list> je lista registara navedena između { } koja ne sme da sadrži Rn

Aritmetičko-logičke instrukcije. (x86-64, ARM)

TODO

Instrukcije bezuslovnog skoka. (x86-64, ARM)

TODO

- Flegovi procesora

(O, S, Z, C). Kada se postavljaju i čemu služe?- Postavljaju se nakon određenih operacija

Kod

x86-64se to radi automatski, npr.cmp eax, edi ; biće updateovani O, S i Z flegovi add eax, esi ; biće updateovani O, Z, C flegovi PROVERI

Kod

ARMse to radi tako što se dodaje sufikssna operacije kojima to po default-u nije takocmp r0, r1 ; biće updateovani O, S i Z flegovi adds r0, r2 ; biće updateovani O, Z, C flegovi PROVERI

O(overflow) - prekoračenje kod označenih operatora- govori da li je došlo do prekoračenja

S(sign) - najveći bit rezultata- govori da li je broj negativan ili nenegativan (\(x < 0 \ \lor x \leq 0\))

Z(zero)- govori da li je rezultat prethodne operacije \(0\)

C(carry)- govori da li je došlo do prenosa na bitu najveće težine

- Postavljaju se nakon određenih operacija

Instrukcije poređenja i njihova uloga u realizaciji uslovnih skokova. (x86-64, ARM)

TODO

Instrukcije uslovnog skoka. (x86-64, ARM)

TODO

- Koju kombinaciju flegova testira instrukcija

jl, a kojujbnax86-64arhitekturi?jl: \(S \oplus O\)jb: \(C\)

Objasniti pozivanje procedura i vraćanje iz njih korišćenjem steka za čuvanje povratne adrese. Prednosti i mane.

Pre pozivanja procedure na stek se čuva povratna adresa. Kada se procedura izvrši, instrukcija povratka uzima vrednost povratne adrese sa steka kako bi povratila kontrolu instrukciji koja sledi nakon zvanja procedure.

Mane:

- sporije nego čuvanje u registrima

Prednosti:

- nemamo ograničen broj parametara koji možemo čuvati na steku što je pogodno za rekurzivne procedure

Objasniti pozivanje procedura i vraćanje iz njih korišćenjem registara za čuvanje povratne adrese. Prednosti i mane.

Pre pozivanja procedure u poseban registar se čuva povratna adresa. Kada se procedura izvrši, instrukcija povratka uzima vrednost povratna adrese iz tog registra kako bi povratila kontrolu instrukciji koja sledi nakon zvanja procedure.

Mane:

- imamo ograničen broj parametara koji možemo čuvati zbog ograničenog broja registara

Prednosti:

- brže nego čuvanje na steku

Objasniti prenos argumenata procedure korišćenjem steka. Prednosti i mane.

Parametri se postavljaju na stek i pozvana procedura mora da ih vrati.

Mane:

- sporije nego registarski

Prednosti:

- nemamo ograničen broj parametara, što je pogodno za rekurzivne procedure

Objasniti prenos argumenata procedure korišćenjem registra procesora. Prednosti i mane.

Pre pozivanja procedure vrednosti koje bi trebalo da joj prosledimo stavljamo u registre koje će koristiti pozvana procedura

Mane:

- imamo ograničen broj parametara zbog ograničenog broja registara

Prednosti:

- brže nego čuvanje na steku

Na koji način pozvana funkcija može vratiti vrednost pozivajućoj funkciji?

Putem steka i registara.

Objasniti pozivanje funkcija na

x86-64arhitekturi. Kako se prenosi adresa povratka, argumenti, kao i povratna vrednost?Prvih 6 argumenata se prosleđuju redom u registre:

rdirsirdxrcxr8r9U slučaju da nam je potrebno više od 6 argumenata, postavljamo ih na stek zdesna ulevo.

Povratna vrednost se čuva u registru

rax.mov edi, 42 mov esi, 7 call f add r10d, eax ; sum += eax

Instrukcija

callpostavlja adresu sledeće instrukcije na stek kao adresu povratka.

Objasniti pozivanje funkcija na

ARMarhitekturi. Kako se prenosi adresa povratka, argumenti, kao i povratna vrednost?Prvih 4 argumenata se prosleđuju redom u registre:

r0r1r2r3U slučaju da nam je potrebno više od 4 argumenata, postavljamo ih na stek zdesna ulevo.

Povratna vrednost se čuva u registru

r0.mov r0, 42 mov r1, 7 bl f add r4, r0 ; sum += eax

Instrukcija

blpostavlja adresu sledeće instrukcije ulr(link register) kao adresu povratka.

9 Procesor

- Koje su osnovne komponente procesora? Objasniti ih.

ALU- Aritmetičko logička jedinica- zadužena je za aritmetičke i logičke operacije nad podacima

- kombinatorno kolo

- obradu podataka vrši isključivo nad registrima

- danas se ne implementira kao jedinstvena komponenta, već iz nekoliko specijalizovanih podjedinica

CU- Kontrolna jedinica- zadužena je za kontrolu redosleda izvršavanja operacija u

ALUi kontrolu prenosa podataka i instrukcija iz i u procesor. - sekvencijalno kolo

- zadužena je za kontrolu redosleda izvršavanja operacija u

- Registri

- služe za privremeno čuvanje i obradu podataka i adresa

- implementiraju se pomoću statičke memorije

- delimo ih na:

- registre opšte namene

- dostupni su programeru da sa njima radi

- registre specijalne namene

- nisu dostupni programeru jer ih procesor koristi za svog čuvanje stanja itd.

- registre opšte namene

- Šta je

ALUi čemu služi?ALU- Aritmetičko logička jedinica- zadužena je za aritmetičke i logičke operacije nad podacima

- kombinatorno kolo

ALUobradu podataka vrši isključivo nad registrima- danas se ne implementira kao jedinstvena komponenta, već iz nekoliko specijalizovanih podjedinica

Šta su registri opšte namene i čemu služe?

Registri opšte namene su procesorski registri kojima programer ima pristup, nad kojima je moguće vršiti računanje i privremeno čuvanje podataka.

Čemu služi instrukcioni registar

IR?IRsadrži instrukciju koja se trenutno izvršava ili dekodira.Spada u registre specijalne namene, odnosno nije registar opšte namene.

Čemu služi programski brojač

PC?PCsadrži adresu naredne instrukcije koja treba da se izvrši.Spada u registre specijalne namene, odnosno nije registar opšte namene.

Čemu služi statusni registar

PSW?PSW= Program Status WordPSWsadrži informacije o trenutnom stanju (state) procesora, odnosno flegove.Spada u registre specijalne namene, odnosno nije registar opšte namene.

Čemu služi registar memorijskih adresa

MAR?MAR= memory adress registerMARsadrži memorijsku adresu sledećeg podataka ili instrukcije koji će procesor da obradi ili da sačuva na to mesto.Predstavlja medijum komunikacije između procesora i adresne magistrale.

Spada u registre specijalne namene, odnosno nije registar opšte namene.

Čemu služi registar memorijskih podataka

MDR?MDR= memory data registerMDRsadrži vrednost sledećeg podataka koji će procesor da obradi ili da sačuva negde u memorijiPredstavlja medijum komunikacije između procesora i data magistrale.

Spada u registre specijalne namene, odnosno nije registar opšte namene.

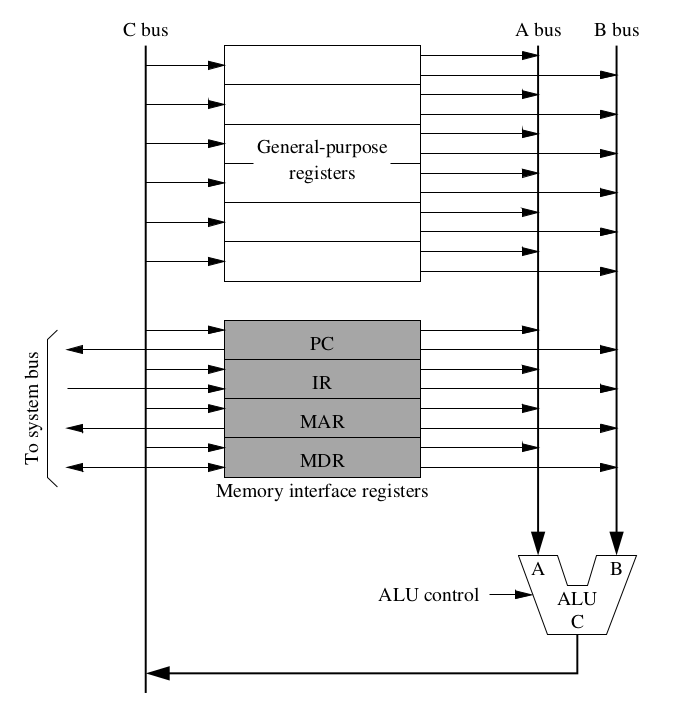

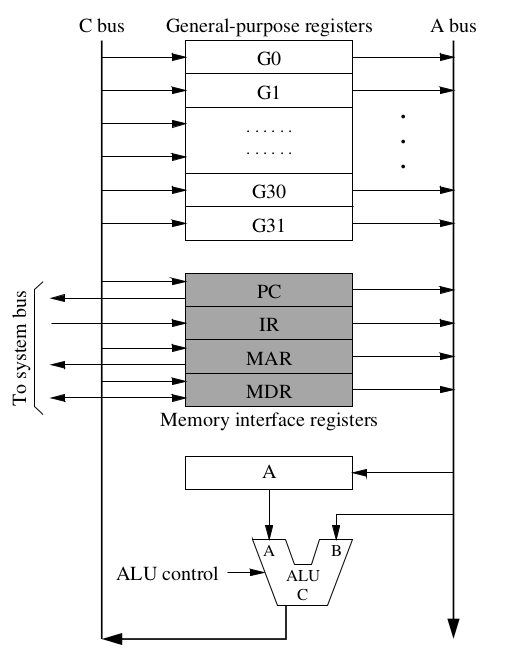

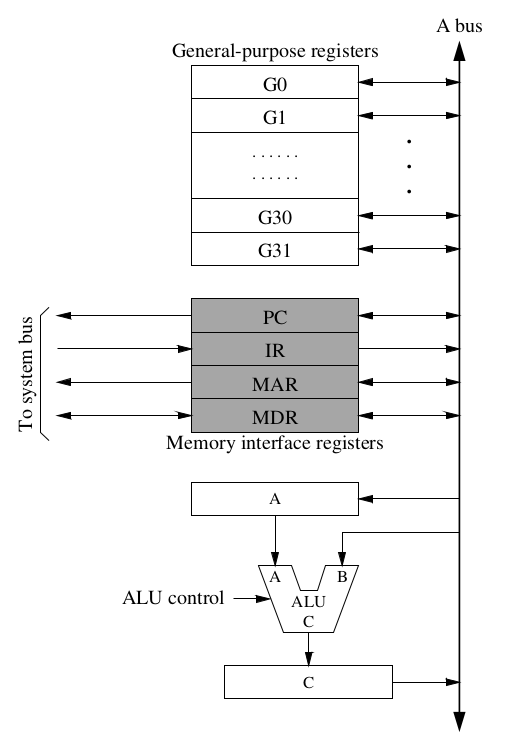

Šta je putanja podataka (datapath) i iz čega se sastoji?

Datapath je deo procesora koji se sastoji iz registara,

ALU-a i internih magistrala koje ih međusobno povezuju koji je zadužen za transformisanje podataka.Nacrtati uopštenu shemu putanje podataka sa tri interne magistrale. Primer izvršavanja operacije.

Nacrtati uopštenu shemu putanje podataka sa dve interne magistrale. Primer izvršavanja operacije.

Nacrtati uopštenu shemu putanje podataka sa jednom internom magistralom. Primer izvršavanja operacije.

Šta je kontrolna jedinica (

CU)? Šta je ulaz, a šta izlaz kontrolne jedinice?Kontrolna jedinica je komponenta procesora koja pomoću kontrolnih signala govori datapath-u šta da uradi sa podacima

Uloga

CUje:- koordinacija podataka iz, u i među procesorskim podjedinicama

- interpretiranje instrukcija

- kontrola toka podataka u procesoru

- generisanje kontrolnih signala na osnovu instrukcija

Ulazu u

CUse obavlja prihvatanjem podataka iz prihvatnog registra u dekoder, dok je izlaz odCUzapravo izlaz iz dekodera koji je spojen sa ulazomALU-a.Opisati osnovne faze pri izvršavanju instrukcija procesora.

Program čini skup instrukcija koje su smeštene u memoriji. Procesor čita redom instrukcije iz memorije, zatim ih izvršava pa prihvata narednu. Proces se ponavlja sve dok je računar upaljen. Ovaj ciklus je poznat kao pribavi-dekodiraj-izvrši (fetch-decode-execute).

- Objasniti fazu dohvatanja instrukcije

- Adresa zapisana u

PCse kopira uMAR, nakon čega sePCinkrementira. - Kopira se vrednost iz adrese koja je sačuvana u

MARi smešta se uMDR Eventualno, vrednost iz

MDRse kopira uIRnakon čega je faza dohvatanja gotovaPseudo-asembler kod

mov mar, pc inc pc mov mdr, [mar] mov ir, mdr

- Adresa zapisana u

- Objasniti fazu dekodiranja instrukcije

- Kodirana instrukcija u

IRse dekodira - Zajedno sa upravljačkim signalima, dekodirana instrukcija se šalje dalje na

ALUza obradu

- Kodirana instrukcija u

- Objasniti fazu izvršavanja instrukcije

- Na ulaze se dovode operandi, dok se na upravljačke linije dovodi kod operacije

- Kao izlaz dobijamo obrađene podatke

- Na koje načine se može realizovati kontrolna jedinica? Poređenje.

- Hardverski

- implementira se kroz upotrebu sekvencijalnih logičkih jedinica, zbog čega se dobija komplikovanija struktura sa povećanjem instrukcija

- koriste se u

RISCarhiterkturi - rade velikom brzinom, ali broj instrukcija koje mogu da implementiraju je ograničen

- skuplja izrada

- Mikroprogramski

- jednostavnija struktura

- koriste se u

CISCarhitekturi - rade sporije u odnosu na hardverski zbog dodatnog sloja apstrakcije u vidu mikroinstrukcija, ali je lakše izmeniti same instrukcije

- jeftinija izrada

- Hardverski

- Objasniti tvrdo ožičenu (hardversku) implementaciju

CU- implementira se kroz upotrebu sekvencijalnih logičkih jedinica, zbog čega se dobija komplikovanija struktura sa povećanjem instrukcija

- koriste se u

RISCarhiterkturi - rade velikom brzinom, ali broj instrukcija koje mogu da implementiraju je ograničen

- skuplja izrada

- danas se retko koriste

Objasniti mikroprogramsku (softversku) implementaciju

CU- jednostavnija struktura

- koriste se u

CISCarhitekturi - rade sporije u odnosu na hardverski zbog dodatnog sloja apstrakcije između hardvera i mašinskih instrukcija, no lakše je izmeniti instrukcije

- jeftinija izrada

- danas se praktično uvek koriste

Mikroprogram, koji se sastoji iz mikroinstrukcija sačuvan je u posebnoj

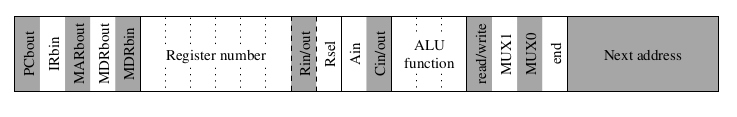

ROMiliPLAmemorijiCU-a. Izvršavanje mikroinstrukcija generiše skup kontrolnih signala.Šta je mikroinstrukcija? Struktura mikroinstrukcije

Mikroinstrukcija je najmanja celina mikrokoda koji predstavlja programibilni sloj apstrakcije između hardvera i mašinskog koda. Struktura mikroinstrukcije može biti horizontalna i vertikalna

Šta je mikroprogram? Objasniti način izvršavanja mikroprograma.

Mikroprogram je niz mikroinstrukcija. Ideja mikroprogama je da se mašinske instrukcije pretvore u mikrorutine (niz mikroinstrukcija koji odgovara jednoj mašinskoj instrukciji) čije mikroinstrukcije se čuvaju u

ROMiliPLAmemoriji, čije izvršavanje generiše odgovarajuće kontrolne signale.Mikroprogram se izvršava od strane mikroprogramskog kontrolera.

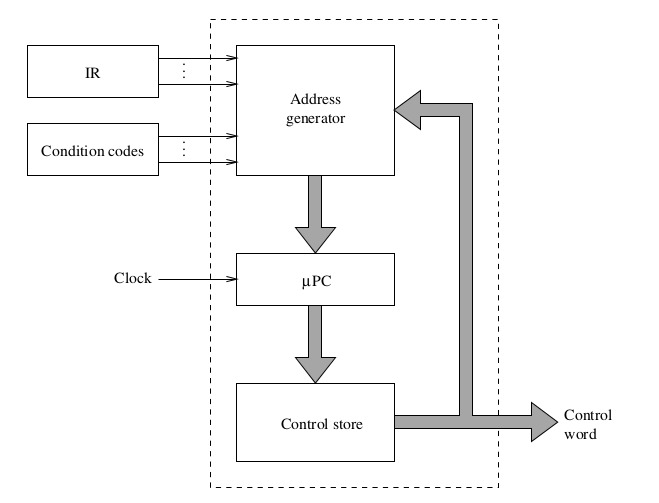

Figure 21: Mikrokontroler

- adress generator - dobija instrukciju od \(IR\) i flegove na osnovu kojih generiše adresu odgovarajuće mikroinstrukcije (adresa u control store-u)

- \(\mu PC\) - slično kao \(PC\) (čuva sledeću mikroinstrukciju koju treba izvršiti)

- control store -

ROMiliPLAmemorija gde se nalaze same mikroinstrukcije

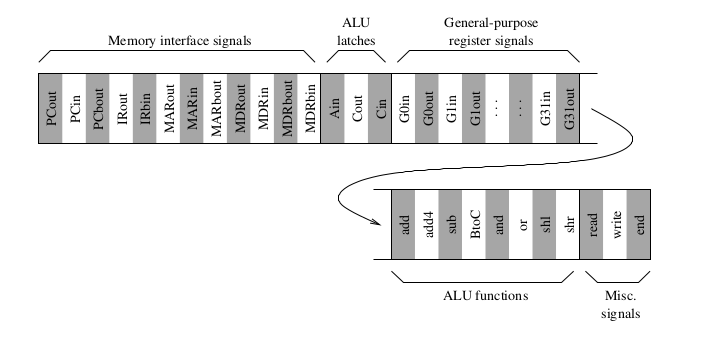

Objasniti horizontalni format mikroinstrukcija procesora.

Figure 22: Horizontalni format

Horizontalni format:

- svakom signalu odgovara po jedan bit

- samim tim, nije potrebno nikakvo dekodiranje jer možemo direktno pročitati vrednost

- Prednosti:

- moguće je navođenje velikog broja signala u jednoj instrukciji, zbog čega nam je potrebno manje ciklusa za izvršavanje instrukcija

- Mane:

- veličina mikroinstrukcije (npr. 90 bitova)

- svakom signalu odgovara po jedan bit

Objasniti vertikalni format mikroinstrukcija procesora.

Vertikalni format:

Vertikalni format:

- Na dužini mikroinstrukcije je moguće uštedeti ako bismo umesto npr. 64 bita za kontrolisanje 32 registra (kontrolni signali za ulaz i izlaz svakog) koje bismo koristili u horizontalnom formatu, koristili 5 za identifikovanje registra i 1 za izbor signala (ulaz ili izlaz)

- Prednost

- kraće mikroinstrukcije

- Mane

- u jednom ciklusu je moguće navesti samo jedan registar, zbog čega nam je potrebno više ciklusa za izvršavanje instrukcija

10 Memorija

- Karakteristike memorija.

- kapacitet

- adresivost

- performanse

- trajnost (postojanost) zapisa

- mogućnost promene sadržaja

- promenljivost zapisa

- cena

- fizički tip medijuma

- Navesti moguće načine pristupa memoriji

- sekvencijalni

- direktni (neposredni)

- proizvoljni (slučajni)

- asocijativni

Objasniti sekvencijalni pristup memoriji

Podaci su organizovani u jedinice koje nazivamo slogovi koji su međusobno razdvojeni kontrolnim informacijama (npr. dužina sloga) koje se koriste pri pristupanju određenom slogu.

Podaci se upisuju po redosledu unošenja, a čitaju po istom ili obrnutom redosledu.

Da bi se pristupilo \(i\) -tom slogu potrebno je proći kroz svih prethodnih \(i - 1\) slogova, što znači da je ovaj način dosta spor.

Primer: magnetna traka

Objasniti direktni (neposredni) pristup memoriji (semi-random)

Kod ovog načina pristupa postoji veza između adrese podatka i pozicije njegovog sloga na medijumu. Na osnovu adrese se pristupa lokaciji sloga ili njegovoj okolini. Vreme pristupa je promenljivo i zavisi od pozicije na medijumu.

Primer: magnetni disk

Objasniti proizvoljni (slučajni) pristup memoriji (Random Access Memory)

Kod ovakvog načina pristupa moguće je u konstantnom vremenu pristupiti bilo kojoj adresibilnoj lokaciji nezavisno od toga gde se fizički nalazi.

Primer: glavna memorija (

RAM)Objasniti asocijativni pristup memoriji (Content Adressable Memory)

Ovo je podtip proizvoljnog pristupa memoriji koji omogućava pretragu cele memorije na osnovu dela sadržaja (reči) umesto pomoću adrese.

Primer: koristi se kod specijalizovanih baza podataka

Šta je kapacitet memorije i u kojim jedinicama se izražava?

Kapacitet predstavlja količinu podataka koji se mogu sačuvati u memoriji.

Obično se izražava u

KiB, MiB, GiB, TiB- Kakva memorija može biti s obzirom na trajnost (postojanost) zapisa? Primeri.

- Privremena

- gube zapis s nestankom napajanja

- Stalna

- čuvaju zapis sve dok ne dođe do namerne promene (ignorišemo fizičko degradiranje materijala itd.)

- Privremena

- Kakva memorija može biti s obzirom na promenjivost sadržaja? Primeri.

- promenljive

- memorija koja se koristi za implementaciju registara i

RAM

- memorija koja se koristi za implementaciju registara i

- polu-promenljive

PROM, EPROM, EEPROM

- nepromenljive

ROM

- promenljive

Kako se izražava brzina memorije? Koji faktori najviše utiču na brzinu memorije?

Izražava se u količini obrađenih podataka po jedinici vremena. Kod RAM memorija se često izražava u \(MHz\).

Najviše utiču:

- način adresiranja

- tehnologija izrade

Objasniti hijerarhiju memorija

TODO

Smara, stvarno treba da se ranim ako ne budem znao ovo.

Šta je

ROM? Kakve vrste postoje? Gde se koristi?ROMje read-only memorija čiji sadržaj je stalan i ne može se menjati (u klasičnom smislu). Implementira se kao kombinatorno kolo jer vrednosti na izlazu zavise isključivo od vrednosti na ulazu.Najčešće se koristi za smeštanje low-level programa i mikrokoda koji su potrebni za pokretanje računara.

Vrste:

ROM: Read Only MemoryPROM: Programmable Read Only MemoryEPROM: Erasable Programmable Read Only MemoryEEPROM: Electrically Erasable Programmable Read Only MemoryFlash(jako sličnoEEPROM-u s tim što dozvoljava brisanje više bajtova odjednom)

Šta je

RAM? Kakve vrste postoje?RAM(Random Access Memory) je memorija sa slučajnim pristupom.Sadržaj memorije se gubi bez napajanja. Moguće je proizvoljan broj puta čitati i pisati iz iste memorije.

Vrste:

- statički

- dinamički

Šta je statički

RAMi koje su njegove osnovne karakteristike? Gde se koristi?SRAMje vrstaRAM-a koja se najčešće koristi za implementaciju keš memorije i registara procesora.Najčešće se implementiraju pomoću D-flip-flopova i nekih drugih kombinatornih kola.

Karakteriše ga velika brzina čitanja i pisanja, ali takođe i velika cena izrade, zbog čega se i rezervisano koriste.

Šta je dinamički

RAMi koje su njegove osnovne karakteristike? Gde se koristi?DRAMje vrstaRAM-a koja se najčešće koristi za implementaciju glavne memorije u računaru (u “narodnom” shvatanjuRAM).Jedna memorijska jedinica je sačinjena od jednog tranizstora i kondenzatora, što ga čini dosta jeftinim za proizvodnju, kao i kompaktnim za ređanje velikog broja memorijskih ćelija na malom prostoru.

Mana

DRAM-a je što je potrebno relativno često ažurirati vrednosti jer se vremenom gube iz kondenzatora. Takođe, pri čitanju se vrednost uništava, pa ju je potrebno opet upisati nakon čitanja.Šta su isprepletane memorije? Objasniti.

To je jedna od tehnika koja se koristi za smanjenje kašnjenja prilikom pristupa susednim memorijskim adresama.

Ideja je da se memorija izdeli na nekoliko manjih uzastopnih memorijskih jedinica koje nazivamo bankama. Ulazne adrese izdelimo u dva dela \(m\) (viši bitovi) i \(k\) (niži bitovi), tako da \(k\) služi da identifikuje banku, dok \(m\) služi da identifikuje adresu u toj banci. Na taj način možemo paralelno pristupati različitim bankama i da smanjimo vreme koje nam je potrebno za pristupanje memoriji.

Koje vrste preslikavanja memorijskih adresa razlikujemo? Objasniti.

Preslikavanje adresa je postupak kojim mapiramo fizičku memoriju u adresnom prostoru računara.

Preslikavanje može biti puno i delimično

Objasniti puno preslikavanje memorijskih adresa.

Puno preslikavanje memorijskih adresa je

1-1preslikavanje (za svaku memorijsku lokaciju postoji najviše jedna adresa koja joj odgovara)Objasniti delimično preslikavanje memorijskih adresa

Puno preslikavanje memorijskih adresa nije

1-1preslikavanje (za svaku memorijsku lokaciju postoji više adresa koje joj odgovaraju)Objasniti poravnanje podataka (memorija).

Procesori čitaju podatke u rečima. Ako imamo poravnate podatke to znači da je moguće samo u jednom ciklusu pročitati reč u kojoj se nalazi naš podatak. Kada ne bismo imali poravnate podatke, uštedeli bismo malo na memoriji, ali bismo dosta izgubili na performansama, ne samo zbog većeg broj utrošenih ciklusa za čitanje već i zbog promašaja u kešu.

Navesti osnovne vrste spoljašnjih memorija i navesti njihove karakteristike

Spoljašnja memorija trajno sadrži podatke i programe koji se ne koriste aktivno (nije joj potrebno napajanje za očuvanje sadržaja). Dosta je sporija od unutrašnje memorije, ali ima veći kapacitet.

Primeri:

- magnetna traka

- magnetni diskovi (floppy, HDD)

- optički diskovi (CD, DVD, BlueRay)

- flash drive, SSD

11 Cache

Objasniti namenu i osnovni princip rada keša.

Keš memorija predstavlja malu količinu brze memorije koja u memorijskoj hijerarhiji stoji između procesorskih registara i glavne memorije i služi da ublaži razliku u brzini između procesora i glavne memorije.

Implemenitraju se preko

SRAM-a. Funkcionišu tako što unapred dobave podatke ili instrukcije za koje se smatra da postoji velika verovatnoća da će procesoru trebati, zbog čega se u slučajevima kada se pogodi, dosta smanjuje vreme potrebno za neku operaciju.Objasniti princip lokalnosti. Šta je prostorna a šta vremenska lokalnost? Primeri.

Prostorna lokalnost je tendencija naših programa da se podacima i instrukcija pristupa sekvencijalno.

Primeri:

- u C-u niz predstavlja uzastopni blok memorije, te on zadovoljava princip prostorne lokalnosti

- instrukcije najčešće se izvršavaju sekvencijalno, osim ako imamo skokove

Vremenska lokalnost je tendencija naših programa da ponovno koriste iste instrukcije ili podatke.

Primer:

- ako imamo program koji računa sumu niza, onda se promenljiva koja čuva sumu može staviti u keš zajedno sa instrukcijama u petlji

Na koji način keš koristi principe prostorne i vremenske lokalnosti?

Keš memorije koriste princip prostorne lokalnosti tako što kopiraju celu okolinu nekog podatka/instrukcije iz glavne memorije iako je samo jedan podatak tražen jer se očekuje da će i susedni podaci biti uskoro korišćeni.

Princip vremenske lokalnosti ostvaruje se tako što se podaci/instruckije koji su nedavno korišćeni nalaze u kešu, jer je pretpostavka da će uskoro biti ponovo korišćeni.

Objasniti čitanje keša u slučaju pogotka

Čitanje keša u slučaju pogotka znači da smo podatak koji smo tražili od glavne memorije našli u kešu. Magistrale za adrese i podatke se blokiraju i razmena podataka se dešava direktno između procesora i keša. Na ovaj način čitanje je dosta brže.

Objasniti čitanje keša u slučaju promašaja

Ako se traženi podaci ne nalaze u kešu, onda se čitaju iz memorije i istovremeno upisuju u keš. Magistrale za adrese i podatke su aktivne, što znači da se odvija uobičajeno čitanje iz memorije sa dodatnim upisom u keš što ovaj slučaj čini sporijim nego čitanje iz memorije bez prisutva keša.

Objasniti pisanje keša u slučaju pogotka

U slučaju pogodtka postoje dve mogućnosti za pisanje:

- samo u kešu

- i u kešu i u glavnoj memoriji

Objasniti pisanje keša u slučaju promašaja

U slučaju promašaja podaci se upisuju samo u memoriju zato što ne postoje u kešu.

Šta je preslikavanje adresa keša i koje vrste preslikavanja postoje?

blok = uzastopni komad memorije

Preslikavanje adrese keša je mapiranje između blokova iz glavne memorije i keš linija.

Vrste:

- neposredno

- set-asocijativno

- asocijativno

Objasniti neposredno preslikavanje adresa keša i dati primer.

- Svaki blok se mapira u tačno jednu liniju keša

- \(M\) - količina glavne memorije

- \(m\) - količina keš memorije

- \(B\) - veličina jednog bloka memorije (ujedno i veličina jedne linije keša)

- \(A\) - dužina adrese (npr. 32 ili 64 bita)

- \(C = m \ / \ B\) - broj keš linija

- \(c_{i} = i \ mod \ C\) - \(i\) -ti blok memorije se mapira u \(c_{i}\) -tu keš liniju

- Lako je za implementaciju, ali je takođe lako dobiti najgori mogući slučaj

Primer:

- \(M = 64\)

- \(m = 16\)

- \(B = 4\)

- \(A = 32\)

\(C = m \ / \ B = 4\)

i ci 0 0 1 1 2 2 3 3 4 0 5 1 6 2 7 3 8 0 9 1 10 2 11 3 12 0 13 1 14 2 15 3

Svaka adresa iz memorije se deli u 3 dela:

keš tag keš linija id offset - offset

- služi da odredi koji bajt iz linije tražimo

- zauzima \(b = log_{2}(B)\) bitova

- keš linija id

- moduliramo ovaj uzastopni podniz bitova da bismo dobili na koju liniju keša mapiramo dati blok

- zauzima \(c = log_{2}(C)\) bitova

- keš tag

- služi za čuvanje u kešu kako bi keš znao koji blok memorije je u pitanju (pošto se više blokova memorije mogu mapirati u istu keš liniju)

- zauzima \(t = A - b - c\) bitova

U liniji keša čuva se:

validan bit keš tag keš podatak - keš podatak

- podaci kopirani iz mapiranog bloka memorije

- keš tag

- pošto se više blokova memorije mogu mapirati u istu keš liniju, koristimo keš tag da ih razlikujemo

- validan bit

- govori da li keš linija sadrži validne podatke (na početku je nego đubre, pa na ovaj način to naznačavamo)

Kada želimo da proverimo da li se blok nalazi u kešu potrebno je:

- naći “id” keš linije, odonosno \(c_{i}\)

- ako je validan bit jednak \(0\) onda je promašaj

- ako se keš tag i trenutni tag razlikuju onda je promašaj

- u suprotnom nađen je

Slično važi i za upis, koji je dodatno vezan za polisu upisa.

- Svaki blok se mapira u tačno jednu liniju keša

Objasniti asocijativno preslikavanje adresa keša i dati primer.

- Svaki blok je moguće mapirati u bilo koju keš liniju

- Ako koristimo

FIFOalokaciju, onda se faktički novi blok upisuje u prvu sledeću slobodnu liniju. Kada se popuni keš izbacujemo ih redom kojim smo ih uneli. - \(M\) - količina glavne memorije

- \(m\) - količina keš memorije

- \(B\) - veličina jednog bloka memorije (ujedno i veličina jedne linije keša)

- \(A\) - dužina adrese (npr. 32 ili 64 bita)

- \(C = m \ / \ B\) - broj keš linija

- Ako koristimo

Svaka adresa iz memorije se deli u 2 dela:

keš tag offset - offset

- služi da odredi koji bajt iz linije tražimo

- zauzima \(b = log_{2}(B)\) bitova

- keš tag

- služi za čuvanje u kešu kako bi keš znao koji blok memorije je u pitanju (pošto se više blokova memorije mogu mapirati u istu keš liniju)

- zauzima \(t = A - b\) bitova

U liniji keša čuva se:

validan bit keš tag keš podatak - keš podatak

- podaci kopirani iz mapiranog bloka memorije

- keš tag

- pošto se više blokova memorije mogu mapirati u istu keš liniju, koristimo keš tag da ih razlikujemo

- validan bit

- govori da li keš linija sadrži validne podatke (na početku je nego đubre, pa na ovaj način to naznačavamo)

- Kada želimo da proverimo da li se blok nalazi u kešu potrebno je:

- sve linije koje imaju validan bit jednak \(1\) se uzimaju u obzir

- porede se keš tagovi i trenutni tag, ako se ne nađu onda imamo promašaj

- u suprotnom nađen je

- Problem nije veća količina memorije odvojena za keš tag, već činjenica da jedan blok može da bude u bilo kojoj keš liniji, zbog čega nam je potreban \(C\) komparatora što ga čini dosta skupim (komparator za svaku keš liniju).

- Svaki blok je moguće mapirati u bilo koju keš liniju

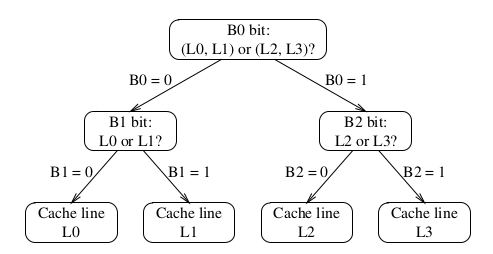

Objasniti skup-asocijativno preslikavanje adresa keša i dati primer.

Skup-asocijativno preslikavanje prestavlja kompromis između

neposrednogiasocijativnogpreslikavanja i kombinaciju tih ideja.- \(M\) - količina glavne memorije

- \(m\) - količina keš memorije

- \(B\) - veličina jednog bloka memorije (ujedno i veličina jedne linije keša)

- \(A\) - dužina adrese (npr. 32 ili 64 bita)

- \(C = m \ / \ B\) - broj keš linija

- \(S \in \{ 2, 4, 8 \}\) - broj disjunktnih skupova

- \(s_{i} = i \ mod \ S\) - \(i\) -ti blok memorije se mapira u \(s_{i}\) -ti skup keš linija

Izdelimo keš linije u disjunktne skupove, kojima pristupamo metodom sličnom kao kod

neposrednogpreslikavanja.- Unutar samih skupova unosimo na proizvoljne keš linije kao kod

asocijativnogpreslikavanja

Svaka adresa iz memorije se deli u 3 dela:

keš tag skup id offset - Unutar samih skupova unosimo na proizvoljne keš linije kao kod

- offset

- služi da odredi koji bajt iz linije tražimo

- zauzima \(b = log_{2}(B)\) bitova

- skup id

- moduliramo ovaj uzastopni podniz bitova da bismo dobili na u koji skup mapiramo dati blok

- zauzima \(s = log_{2}(S)\) bitova

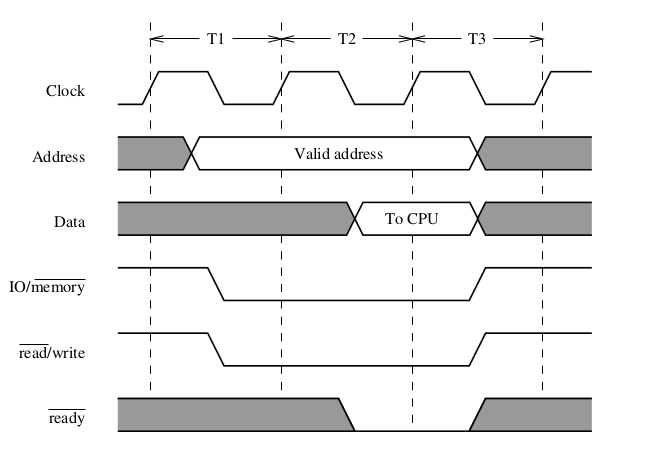

- keš tag